2 reading input data, 3 debouncing inputs, Reading input data - 9 – Kontron CP383 User Manual

Page 55: Debouncing inputs - 10, Cp383 configuration

CP383

Configuration

ID 27784, Rev. 01

© 2004 Kontron Modular Computers GmbH

Page 4 - 9

27784

.01.VC.040308/162544

P R E L I M I N A R Y

4.4.2

Reading Input Data

The input ports are made visible via the Input Data Register. This register reflects the inputs

after them having passed the digital programmable debouncer. An active input appears there

as a logical "1" whereas an open or inactive input port appears as a logical "0". The bit ordering

naturally corresponds with the numbering of the input ports at the connector.

4.4.3

Debouncing Inputs

By default, all inputs are filtered through a passive analog low-pass filter placed immediately

behind the input connector. Additionally, the CP383 provides a programmable digital debounc-

er which is common for all inputs. The input ports are sampled at a programmable sample rate

which is derived from PCI bus clock. Two consecutive samples must be equal before being

stored in the input data register. By this means, bouncing and spikes on inputs can be filtered

out. For example, with a selected input sample rate of 500 Hz, input pulses which are shorter

than 2 ms are filtered out.

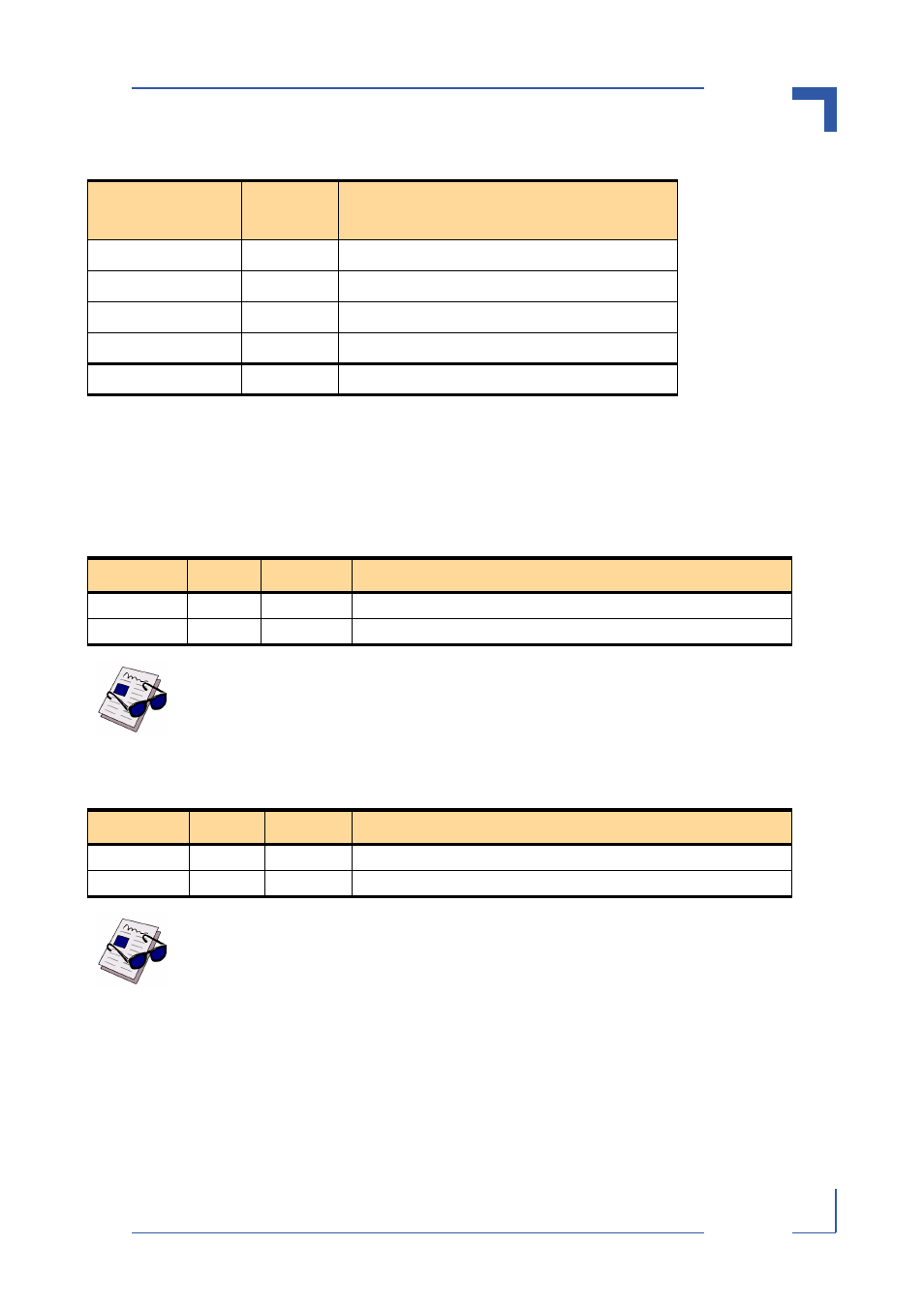

0x441C

32 bit

c_msk

Input Pattern Mask Register

0x4800

32 bit

i_event, Input Status Register

0x4C00

32 bit

d_in,

Input Data Register

0x4C04

32 bit

input,

Transparent Input Data

+ 0x5000

44 kB

Reserved

Table 4-2: Input Data Register

BITS

TYPE

DEFAULT

FUNCTION

31-16

r

0

Reserved

15-0

r

-

Input (debounced)

Note ...

Where the enhanced features such as interrupts, pattern or event detection are

not required, only the input data register is relevant.

Table 4-3: Transparent Input Data Register

BITS

TYPE

DEFAULT

FUNCTION

31-16

r

0

Reserved

15-0

r

-

Input (transparent)

Note ...

In addition to the Input Data Register, there is a second non-latched input regis-

ter (debouncer bypassed).

Table 4-1: Backend Register Address Map (Continued)

BASE ADDRESS

(BAR0)

SIZE

FUNCTION