Chapter 1 – configuration overview, Introduction, Figure 1-1: speedster configuration options – Achronix Bitporter User Manual

Page 7: Chapter 1 – “configuration overview

Bitporter User Guide

PAGE 1

Chapter 1 – Configuration Overview

Introduction

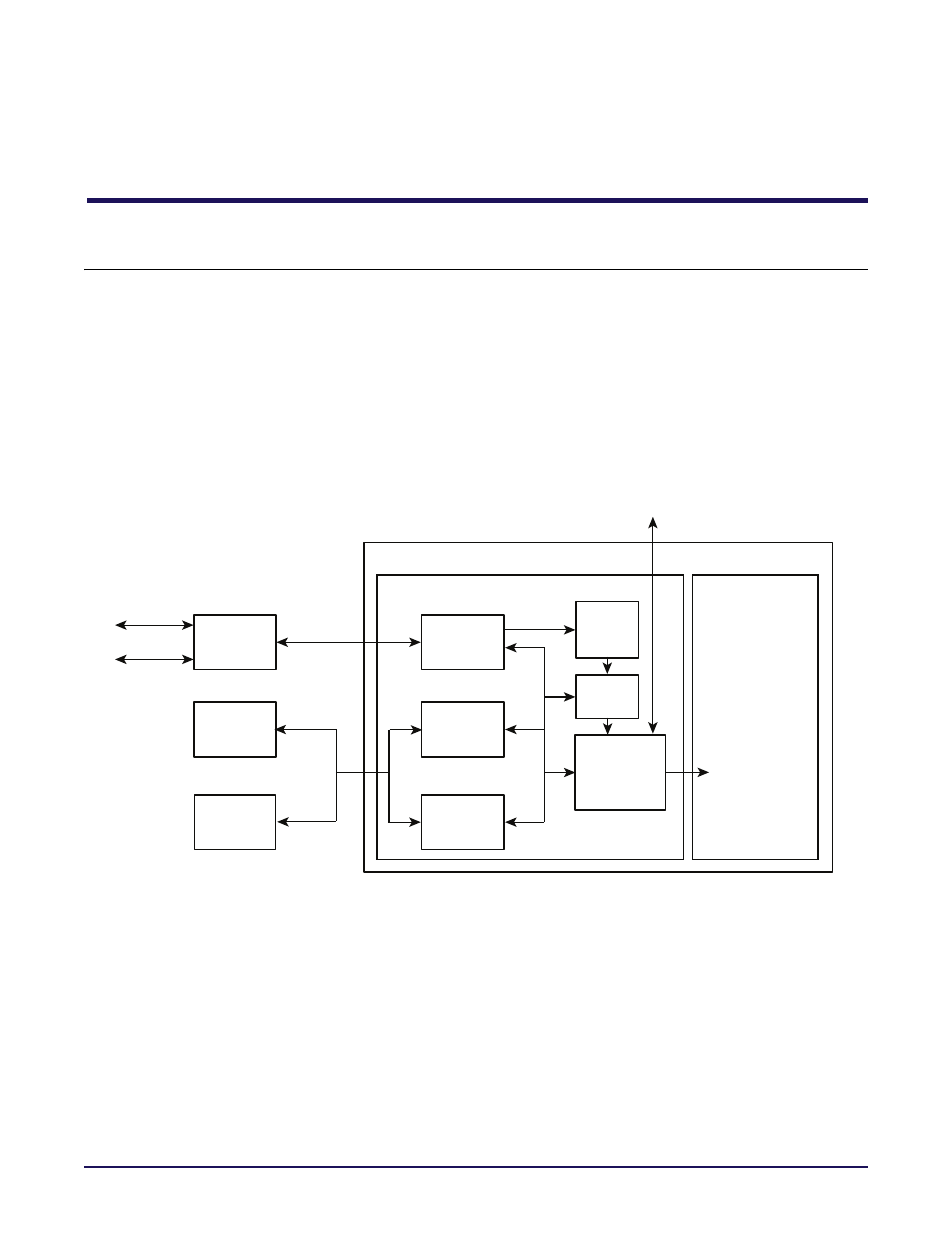

The embedded programming and configuration logic in the FPGA is designed to support a

variety of programming options.

outlines the basic block diagram of the

programming and configuration logic, including additional logic to implement security

features. The configuration management unit controls the startup and shutdown sequence

from configuration mode to the user mode and back. The configuration management unit

includes the provisions for configuring the device with a secure bitstream using a 256‐bit

Advanced Encryption Standard (AES) algorithm in Cipher Block Chaining (CBC) mode. The

device contains a small non‐volatile memory for the storage of the required AES key.

This guide covers configuration via the JTAG port using the Achronix Bitporter pod.

Figure 1-1:

Speedster Configuration Options

Configuration Logic

FPGA

User Logic

JTAG

USB

Bitporter

Pod

JTAG

Interface

External CPU

CPU Slave

Controller

Serial (SPI)

Flash

SPI Flash

Controller

Serial

Data

ug004_c01_01_v04

•

•

FPGA

Configuration

Management

Unit

SRAM Scan

Chain

AES

Decode

AES NV

Key

Storage

Mode and Status Pins

Ethernet