Cypress EZ-OTG CY7C67200 User Manual

Ez-otg™ programmable usb on-the-go, Ez-otg features, Typical applications

EZ-OTG™ Programmable USB

On-The-Go

CY7C67200

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document #: 38-08014 Rev. *G

Revised November 14, 2006

EZ-OTG Features

• Single-chip programmable USB dual-role (Host/Peripheral)

controller with two configurable Serial Interface Engines

(SIEs) and two USB ports

• Supports USB OTG protocol

• On-chip 48-MHz 16-bit processor with dynamically

switchable clock speed

• Configurable IO block supports a variety of IO options or up

to 25 bits of General Purpose IO (GPIO)

• 4K × 16 internal mask ROM contains built-in BIOS that

supports a communication-ready state with access to I

2

C™

EEPROM interface, external ROM, UART, or USB

• 8K x 16 internal RAM for code and data buffering

• 16-bit parallel host port interface (HPI) with DMA/Mailbox

data path for an external processor to directly access all

on-chip memory and control on-chip SIEs

• Fast serial port supports from 9600 baud to 2.0M baud

• SPI supports both master and slave

• Supports 12 MHz external crystal or clock

• 2.7V to 3.6V power supply voltage

• Package option: 48-pin FBGA

Typical Applications

EZ-OTG is a very powerful and flexible dual-role USB

controller that supports a wide variety of applications. It is

primarily intended to enable USB OTG capability in applica-

tions such as:

• Cellular phones

• PDAs and pocket PCs

• Video and digital still cameras

• MP3 players

• Mass storage devices

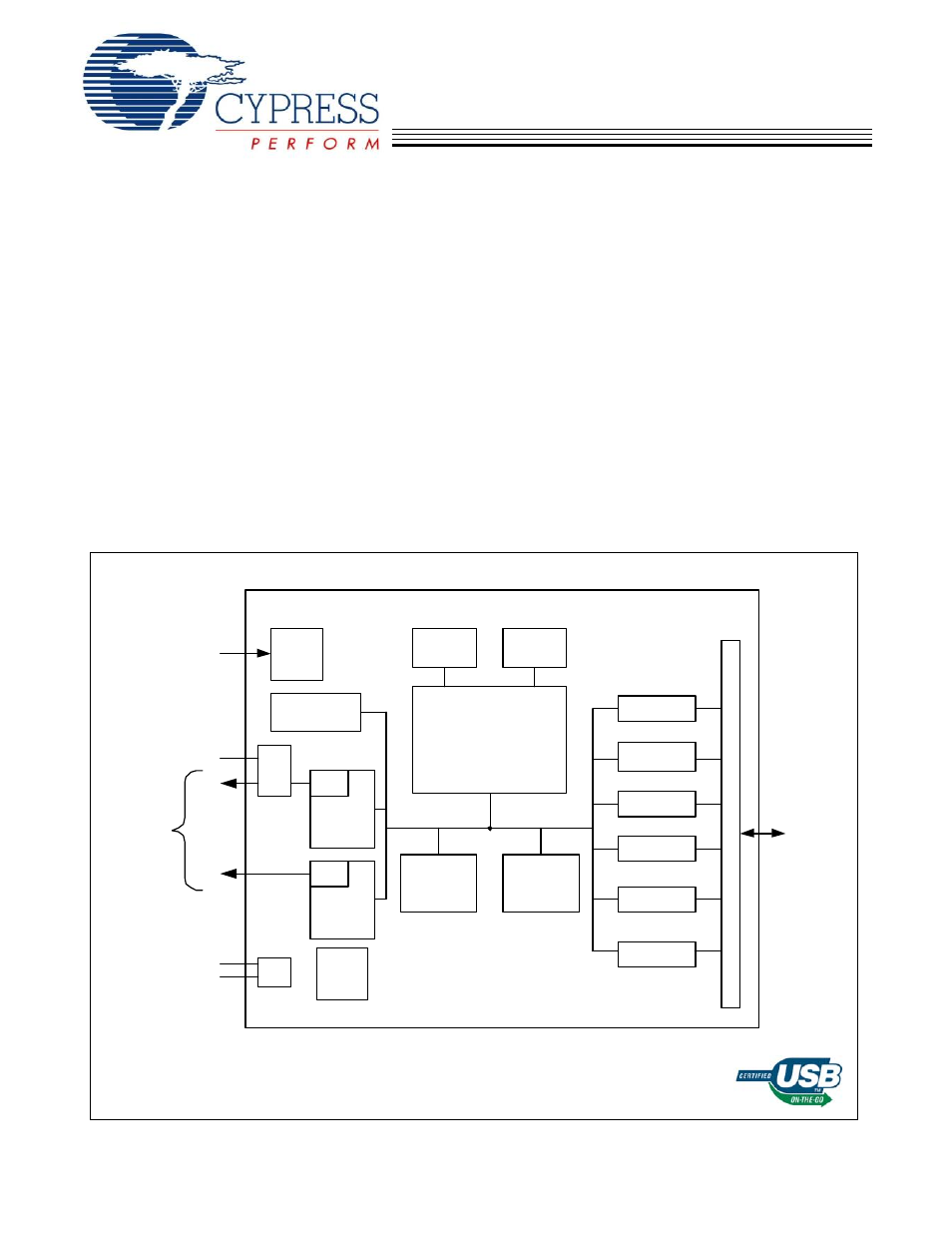

Timer 0

Timer 1

Watchdog

Control

4Kx16

ROM BIOS

8Kx16

RAM

CY16

16-bit RISC CORE

SIE1

USB-A

SIE2

USB-A

OTG

HOST/

Peripheral

USB Ports

D+,D-

D+,D-

UART I/F

HSS I/F

I2C

EEPROM I/F

HPI I/F

SPI I/F

nRESET

CY7C67200

GPIO [24:0]

PLL

X1

X2

GPIO

SH

AR

ED

IN

PU

T/O

U

TPU

T

PIN

S

Vbus, ID

Mobile

Power

Booster

Block Diagram

CY7C67200

Document Outline

- EZ-OTG Features

- Typical Applications

- Introduction

- Processor Core Functional Overview

- Interface Descriptions

- Power Savings and Reset Description

- Memory Map

- Registers

- Processor Control Registers

- Timer Registers

- General USB Registers

- USB Host Only Registers

- Host n Control Register [R/W]

- Host n Address Register [R/W]

- Host n Count Register [R/W]

- Host n Endpoint Status Register [R]

- Host n PID Register [W]

- Host n Count Result Register [R]

- Host n Device Address Register [W]

- Host n Interrupt Enable Register [R/W]

- Host n Status Register [R/W]

- Host n SOF/EOP Count Register [R/W]

- Host n SOF/EOP Counter Register [R]

- Host n Frame Register [R]

- USB Device Only Registers

- Device n Endpoint n Control Register [R/W]

- Device n Endpoint n Address Register [R/W]

- Device n Endpoint n Count Register [R/W]

- Device n Endpoint n Status Register [R/W]

- Device n Endpoint n Count Result Register [R/W]

- Device n Interrupt Enable Register [R/W]

- Device n Address Register [W]

- Device n Status Register [R/W]

- Device n Frame Number Register [R]

- Device n SOF/EOP Count Register [W]

- OTG Control Registers

- GPIO Registers

- HSS Registers

- HSS Control Register [0xC070] [R/W]

- HSS Baud Rate Register [0xC072] [R/W]

- HSS Transmit Gap Register [0xC074] [R/W]

- HSS Data Register [0xC076] [R/W]

- HSS Receive Address Register [0xC078] [R/W]

- HSS Receive Counter Register [0xC07A] [R/W]

- HSS Transmit Address Register [0xC07C] [R/W]

- HSS Transmit Counter Register [0xC07E] [R/W]

- HPI Registers

- SPI Registers

- SPI Configuration Register [0xC0C8] [R/W]

- SPI Control Register [0xC0CA] [R/W]

- SPI Interrupt Enable Register [0xC0CC] [R/W]

- SPI Status Register [0xC0CE] [R]

- SPI Interrupt Clear Register [0xC0D0] [W]

- SPI CRC Control Register [0xC0D2] [R/W]

- SPI CRC Value Register [0xC0D4] [R/W]

- SPI Data Register [0xC0D6] [R/W]

- SPI Transmit Address Register [0xC0D8] [R/W]

- SPI Transmit Count Register [0xC0DA] [R/W]

- SPI Receive Address Register [0xC0DC [R/W]

- SPI Receive Count Register [0xC0DE] [R/W]

- UART Registers

- Pin Diagram

- Pin Descriptions

- Absolute Maximum Ratings

- Operating Conditions

- Crystal Requirements (XTALIN, XTALOUT)

- DC Characteristics

- AC Timing Characteristics

- Register Summary

- Ordering Information

- Package Diagram