Pin diagram, Pin descriptions – Cypress EZ-OTG CY7C67200 User Manual

Page 63

CY7C67200

Document #: 38-08014 Rev. *G

Page 63 of 78

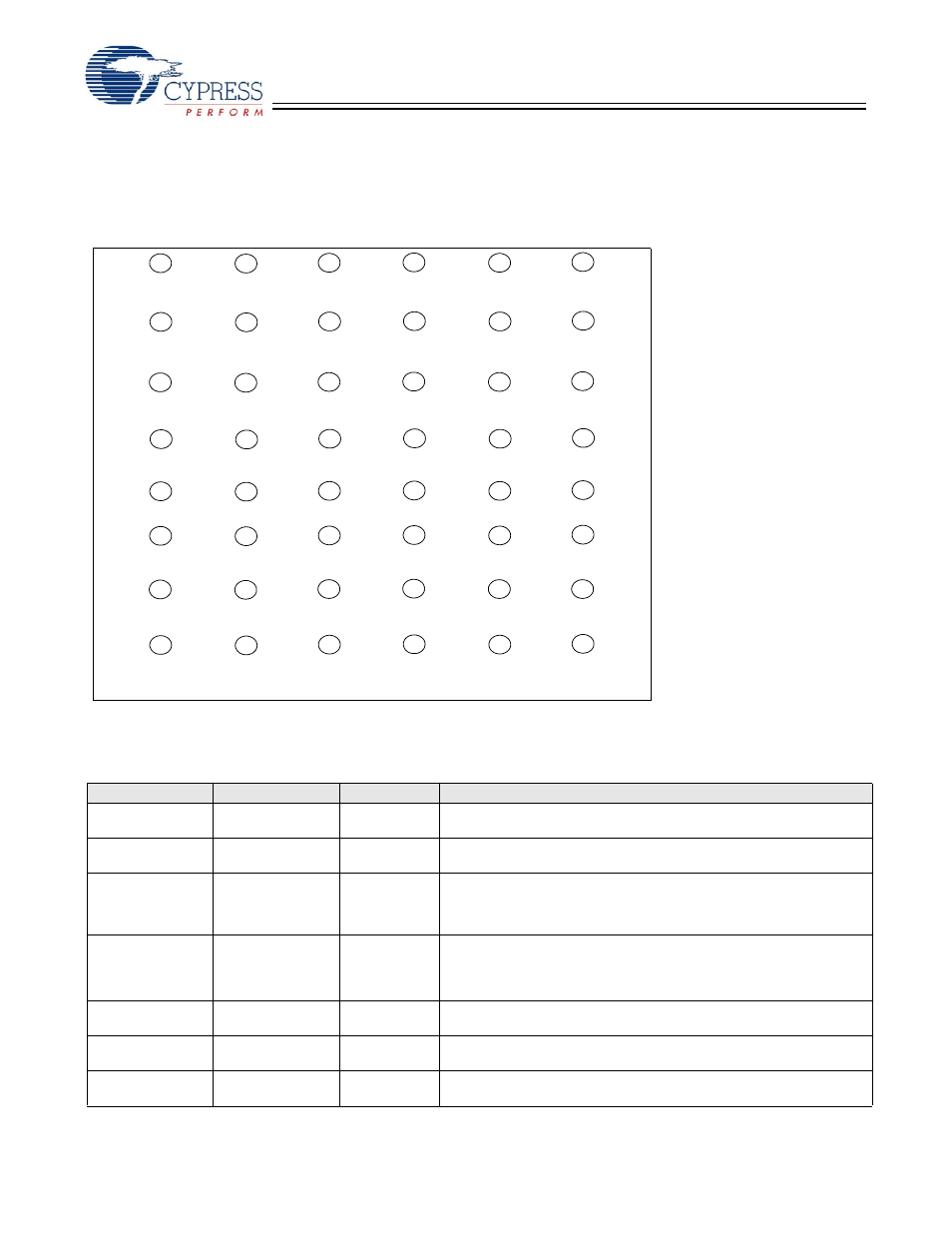

Pin Diagram

The following describes the CY7C67200 48-pin FBGA.

Figure 76. EZ-OTG Pin Diagram

Pin Descriptions

Table 38.Pin Descriptions

Pin

Name

Type

Description

H3

GPIO31/SCK

IO

GPIO31: General Purpose IO

SCK: I2C EEPROM SCK

F3

GPIO30/SDA

IO

GPIO30: General Purpose IO

SDA: I2C EEPROM SDA

F4

GPIO29/OTGID

IO

GPIO29: General Purpose IO

OTGID: Input for OTG ID pin. When used as OTGID, this pin must be

tied high through an external pull-up resistor. Assuming V

CC

= 3.0V, a

10K to 40K resistor must be used.

H4

GPIO24/INT/IRQ0

IO

GPIO24: General Purpose IO

INT: HPI INT

IRQ0: Interrupt Request 0. See Register 0xC006. This pin is also one

of two possible GPIO wakeup sources.

G4

GPIO23/nRD

IO

GPIO23: General Purpose IO

nRD: HPI nRD

H5

GPIO22/nWR

IO

GPIO22: General Purpose IO

nWR: HPI nWR

G5

GPIO21/nCS

IO

GPIO21: General Purpose IO

nCS: HPI nCS

nRESET

A1

A2

A3

A4

A5

A6

B1

B2

B3

B4

B5

B6

H1

H2

H3

H4

H5

H6

G1

G2

G3

G4

G5

G6

F1

F2

F3

F4

F5

F6

E1

E2

E3

E4

E5

E6

D1

D2

D3

D4

D5

D6

C1

C2

C3

C4

C5

C6

GPIO9/D9/

nSSI

Reserved

GND

GND

GPIO3/D3

GPIO1/D1

AGND

VCC

OTGVBUS

GPIO12/D12/

TXD

GPIO13/D13/

RXD

GPIO14/D14/

RTS

DP1A

GND

AVCC

BOOSTVCC

GPIO10/D10/

SCK

DM1A

GPIO0/D0

DM2A

VSWITCH

BOOSTGND

GPIO8/D8/

MISO

GPIO2/D2

GPIO11/D1/

MOSI

DP2A

CSWITCHA

CSWITCHB

GPIO29/

OTGID

GPIO19/A0

GPIO15/D15/

CTS/nSSI

GND

GPIO20/A1

GPIO22/nWR

GPIO21/nCS/

nRESET

GPIO24/INT/

IRQ0

GPIO23/nRD/

nWAIT

GPIO31/SCL

XTALIN

GPIO4/D4

GPIO7/D7/TX

VCC

VCC

GPIO6/D6/RX

GPIO30/SDA

XTALOUT

GPIO5/D5