Host n address register [r/w, Host n count register [r/w – Cypress EZ-OTG CY7C67200 User Manual

Page 21

CY7C67200

Document #: 38-08014 Rev. *G

Page 21 of 78

Host n Address Register [R/W]

• Host 1 Address Register 0xC082

• Host 2 Address Register 0xC0A2

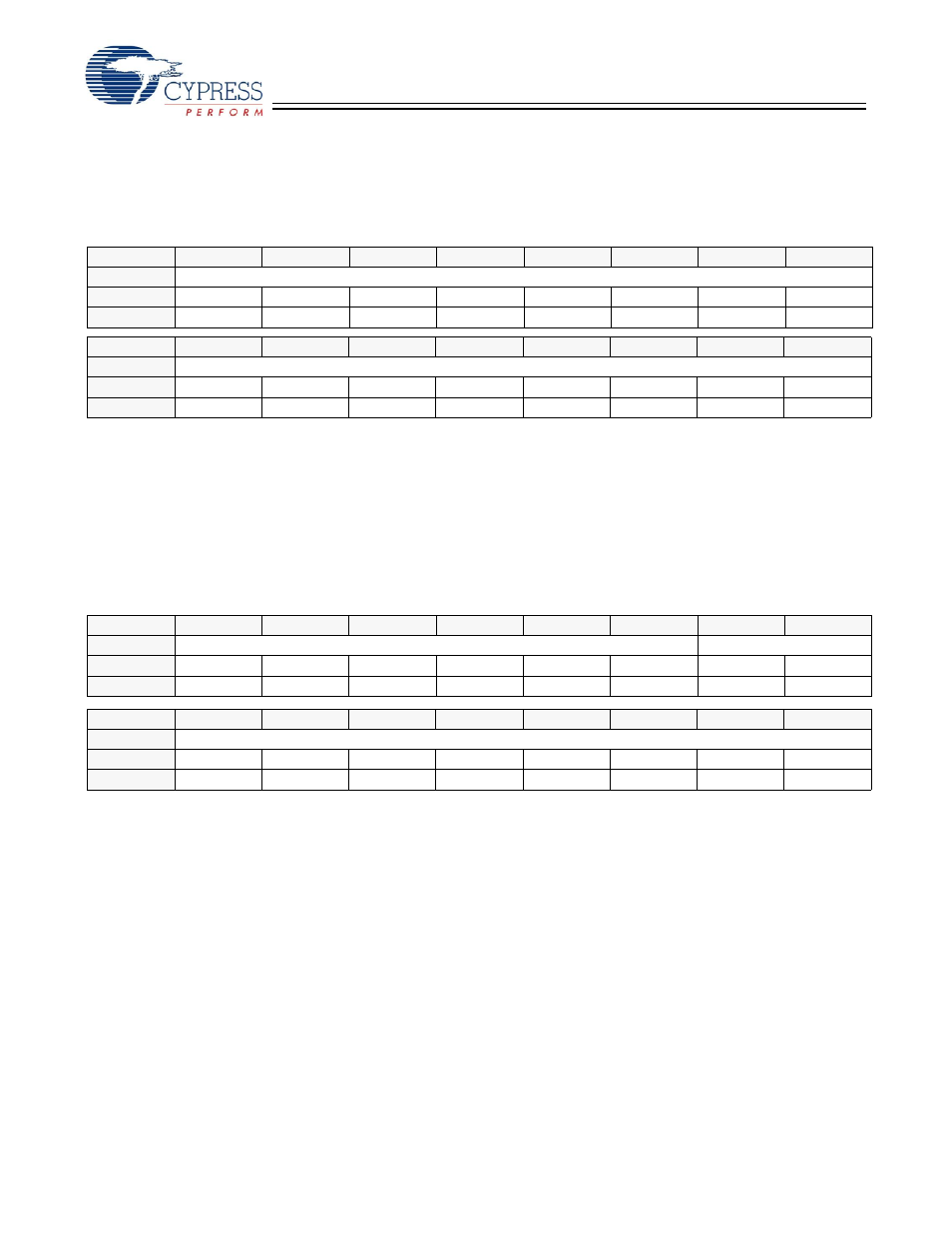

Figure 19. Host n Address Register

Register Description

The Host n Address register is used as the base pointer into

memory space for the current host transactions.

Address (Bits [15:0])

The Address field sets the address pointer into internal RAM

or ROM.

Host n Count Register [R/W]

• Host 1 Count Register 0xC084

• Host 2 Count Register 0xC0A4

Figure 20. Host n Count Register

Register Description

The Host n Count register is used to hold the number of bytes

(packet length) for the current transaction. The maximum

packet length is 1023 bytes in ISO mode. The Host Count

value is used to determine how many bytes to transmit, or the

maximum number of bytes to receive. If the number of

received bytes is greater then the Host Count value then an

overflow condition will be flagged by the Overflow bit in the

Host n Endpoint Status register.

Count (Bits [9:0])

The Count field sets the value for the current transaction data

packet length. This value is retained when switching between

host and device mode, and back again.

Reserved

All reserved bits must be written as ‘0’.

Bit #

15

14

13

12

11

10

9

8

Field

Address...

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

...Address

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit #

15

14

13

12

11

10

9

8

Field

Reserved

Count...

Read/Write

-

-

-

-

-

-

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

...Count

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0