Hpi status port [] [hpi: r – Cypress EZ-OTG CY7C67200 User Manual

Page 52

CY7C67200

Document #: 38-08014 Rev. *G

Page 52 of 78

HPI Status Port [] [HPI: R]

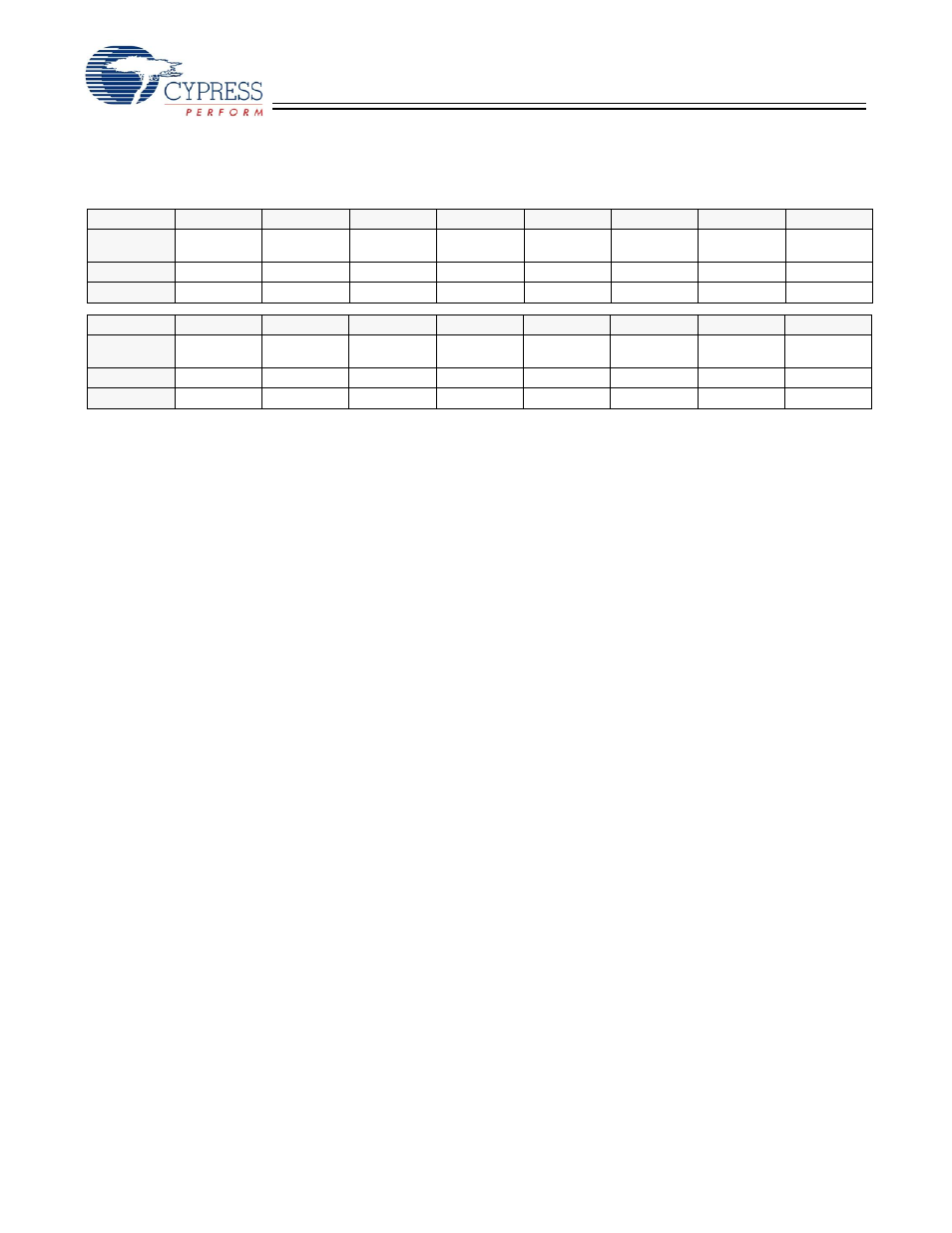

Figure 60. HPI Status Port

Register Description

The HPI Status Port provides the external host processor with

the MailBox status bits plus several SIE status bits. This

register is not accessible from the on-chip CPU. The additional

SIE status bits are provided to aid external device driver

firmware development, and are not recommended for applica-

tions that do not have an intimate relationship with the on-chip

BIOS.

Reading from the HPI Status Port does not result in a CPU HPI

interface memory access cycle. The external host may contin-

uously poll this register without degrading the CPU or DMA

performance.

VBUS Flag (Bit 15)

The VBUS Flag bit is a read-only bit that indicates whether

OTG VBus is greater than 4.4V. After turning on VBUS,

firmware should wait at least 10 µs before this reading this bit.

1: OTG VBus is greater then 4.4V

0: OTG VBus is less then 4.4V

ID Flag (Bit 14)

The ID Flag bit is a read-only bit that indicates the state of the

OTG ID pin.

SOF/EOP2 Flag (Bit 12)

The SOF/EOP2 Flag bit is a read-only bit that indicates if a

SOF/EOP interrupt occurs on either Host/Device 2.

1: Interrupt triggered

0: Interrupt did not trigger

SOF/EOP1 Flag (Bit 10)

The SOF/EOP1 Flag bit is a read-only bit that indicates if a

SOF/EOP interrupt occurs on either Host/Device 1.

1: Interrupt triggered

0: Interrupt did not trigger

Reset2 Flag (Bit 9)

The Reset2 Flag bit is a read-only bit that indicates if a USB

Reset interrupt occurs on either Host/Device 2.

1: Interrupt triggered

0: Interrupt did not trigger

Mailbox In Flag (Bit 8)

The Mailbox In Flag bit is a read-only bit that indicates if a

message is ready in the incoming mailbox. This interrupt

clears when on-chip CPU reads from the HPI Mailbox register.

1: Interrupt triggered

0: Interrupt did not trigger

Resume2 Flag (Bit 7)

The Resume2 Flag bit is a read-only bit that indicates if a USB

resume interrupt occurs on either Host/Device 2.

1: Interrupt triggered

0: Interrupt did not trigger

Resume1 Flag (Bit 6)

The Resume1 Flag bit is a read-only bit that indicates if a USB

resume interrupt occurs on either Host/Device 1.

1: Interrupt triggered

0: Interrupt did not trigger

SIE2msg (Bit 5)

The SIE2msg Flag bit is a read-only bit that indicates if the

CY7C67200 CPU has written to the SIE2msg register. This bit

is cleared on an HPI read.

1: The SIE2msg register has been written by the CY7C67200

CPU

0: The SIE2msg register has not been written by the

CY7C67200 CPU

SIE1msg (Bit 4)

The SIE1msg Flag bit is a read-only bit that indicates if the

CY7C67200 CPU has written to the SIE1msg register. This bit

is cleared on an HPI read.

1: The SIE1msg register has been written by the CY7C67200

CPU

0: The SIE1msg register has not been written by the

CY7C67200 CPU

Done2 Flag (Bit 3)

In host mode the Done2 Flag bit is a read-only bit that indicates

if a host packet done interrupt occurs on Host 2. In device

Bit #

15

14

13

12

11

10

9

8

Field

VBUS

Flag

ID

Flag

Reserved

SOF/EOP2

Flag

Reserved

SOF/EOP1

Flag

Reset2

Flag

Mailbox In

Flag

Read/Write

R

R

-

R

-

R

R

R

Default

X

X

X

X

X

X

X

X

Bit #

7

6

5

4

3

2

1

0

Field

Resume2

Flag

Resume1

Flag

SIE2msg

SIE1msg

Done2

Flag

Done1

Flag

Reset1

Flag

Mailbox Out

Flag

Read/Write

R

R

R

R

R

R

R

R

Default

X

X

X

X

X

X

X

X