Planned certified configurations – Rockwell Automation AADvance Controller Solutions Handbook User Manual

Page 61

Document: 553631

(ICSTT-RM447J_EN_P) Issue: 09:

2-11

CPU A &

CPU B

3 × T9110 Processor Module, T9100 Processor Base Unit,

O/P A

2 × T9451 Digital Output Module, 24V dc, 8 Channel +

9852 Digital Output TA, 24V dc 8 Channel, Dual

Note: All configurations that use dual or triplicate processor modules are suitable for

SIL3 architectures with de-energize to trip outputs. Dual outputs are also required for

SIL3 energize to action outputs.

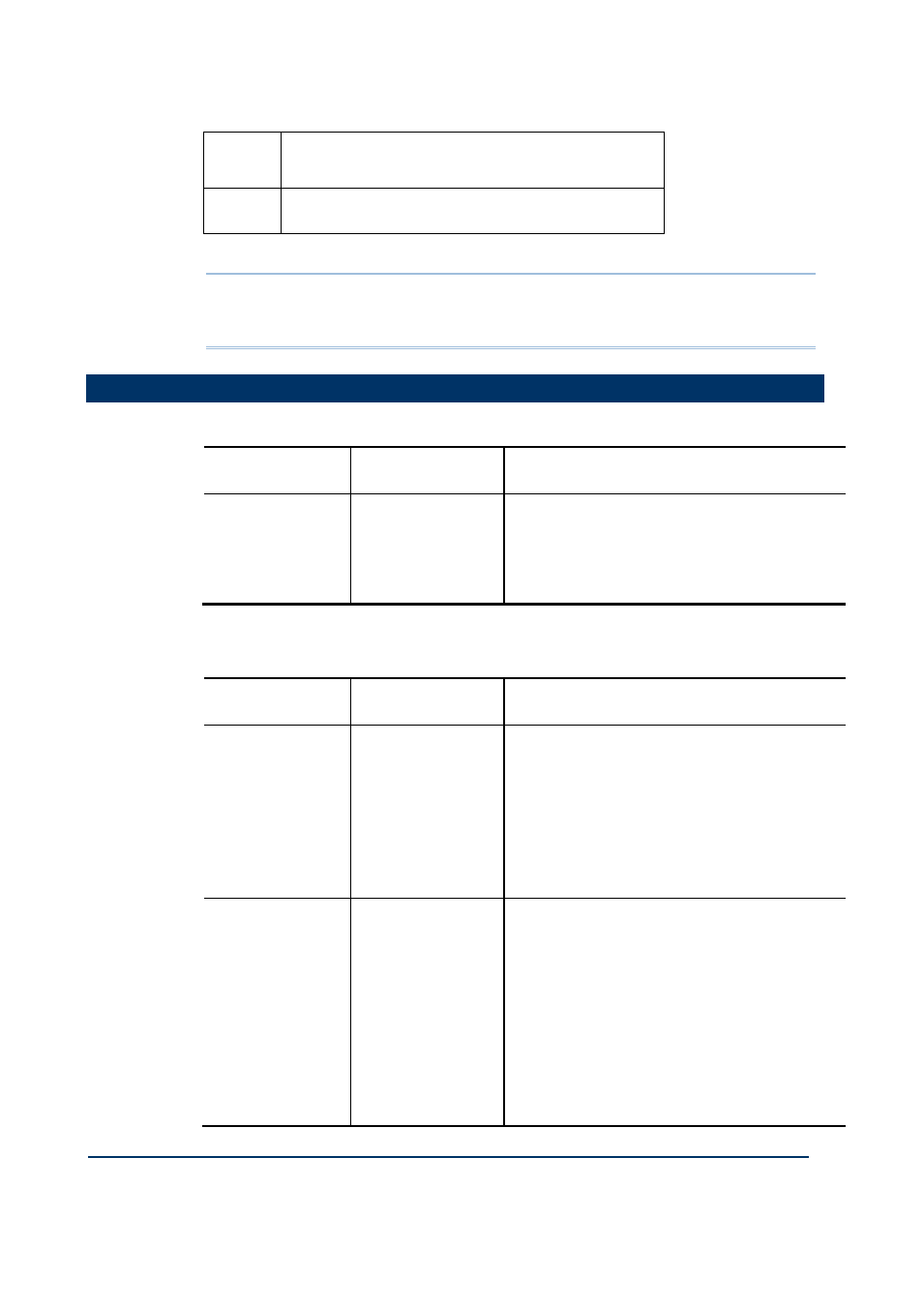

Planned Certified Configurations

Table 12:

Central Modules

Modules

TÜV Certified

Configuration

Conditions

Processor Module

T9110

1oo1D, 1oo2D,

2oo3D

Safety-related and can be used for safety-critical

applications in SIL2 with 1 module fitted and SIL3

applications with 2 or 3 modules fitted.

Note: For High Demand applications you must use

a minimum of two processors.

Table 13:

Input Modules

Modules

TÜV Certified

Configuration

Conditions

Digital Inputs

T9401/2, 24V dc,

8/16 Channel,

isolated.

+

T9801/2/3 Digital

Input TA, 16 channel,

Simplex/Dual/TMR

1oo1D, 1oo2D,

2oo3D

Within a specified safety accuracy limit of 1.0V dc.

De-energized to action (normally energized): SIL3

with 1, 2 or 3 modules fitted.

Energize to action (normally de-energized): with 1, 2

or 3 modules fitted

Note: when the integrity level is at 1oo1D then the

faulty module must be replaced to restore the

integrity level back to 1oo2D.

Analogue Inputs

T9431/2, 8/16

Channel, isolated

+

T9831/2/3 Analogue

Input TA, 16

Channel,

Simplex/Dual/TMR

1oo1D, 1oo2D,

2oo3D

Within the manufactures specified safety accuracy

limits of 200µA. The safety state of the analogue

input has to be set to a safe value which is a

calculated value based on a count value of 0mA.

(refer to the AADvance Configuration Guide Doc

no: 553633 for more details)

SIL3 with 1, 2 or 3 modules fitted.

Note: when the integrity level is at 1oo1D then the

faulty module must be replaced within the MTTR

assumed for the PFD calculations to restore the

integrity level back to 1oo2D.