Table 2-43 an – Ampro Corporation LITTLE BOARD 5001451A User Manual

Page 63

Little Board P6d Module

2-45

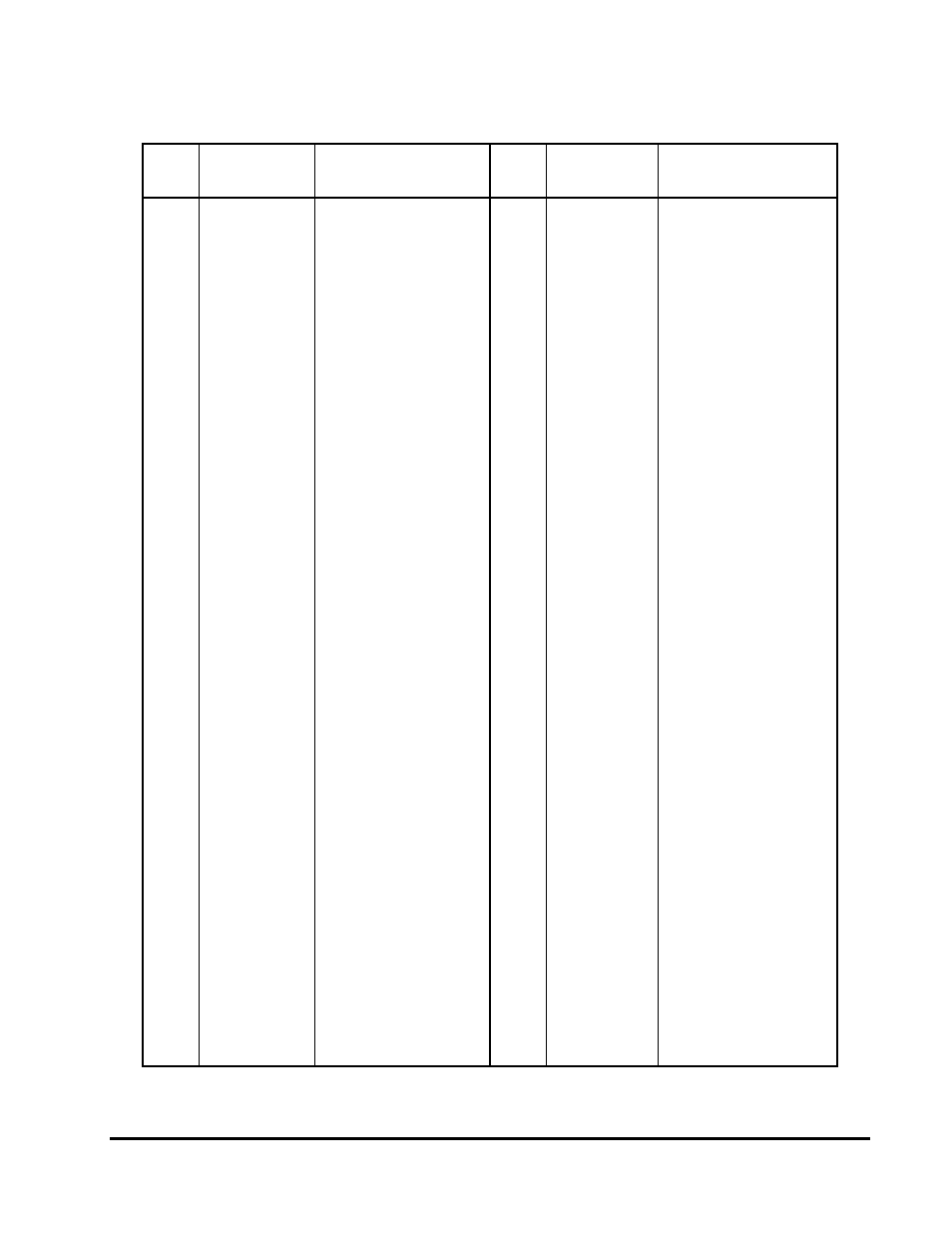

Table 2-43. PC/104 Expansion Bus Connector, J1 (A1-B32)

Pin #

Signal Name

Function

Pin #

Signal

Name

Function

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

IOCHCK*

SD7

SD6

SD5

SD4

SD3

SD2

SD1

SD0

IOCHRDY

AEN

SA19

SA18

SA17

SA16

SA15

SA14

SA13

SA12

SA11

SA10

SA9

SA8

SA7

SA6

SA5

SA4

SA3

SA2

SA1

SA0

GND

Bus NMI input

Data bit 7

Data bit 6

Data bit 5

Data bit 4

Data bit 3

Data bit 2

Data bit 1

Data bit 0

I/O Ready Ctrl

Address Enable

Address bit 19

Address bit 18

Address bit 17

Address bit 16

Address bit 15

Address bit 14

Address bit 13

Address bit 12

Address bit 11

Address bit 10

Address bit 9

Address bit 8

Address bit 7

Address bit 6

Address bit 5

Address bit 4

Address bit 3

Address bit 2

Address bit 1

Address bit 0

Ground

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

GND

RSTDRV

+5V

IRQ9

-5V

DRQ2

-12V

ZWS*

+12V

N/A

SMEMW*

SMEMR*

IOW

IOR

DACK3*

DRQ3

DACK1*

DRQ1

RFSH*

SYSCLK

IRQ7

IRQ6

IRQ5

IRQ4

IRQ3

DACK2*

TC

BALE

+5V

OSC

GND

GND

Ground

System reset signal

+5 Volt power

Interrupt request 9

To J16-3

DMA request 2

To J16-1

Zero wait state

To J10-1

Keyed pin

Mem Write(lwr 1MB)

Mem Read(lwr 1MB)

I/O Write

I/O Read

DMA Acknowledge 3

DMA Request 3

DMA Acknowledge 1

DMA Request 1

Memory Refresh

Sys Clock

Interrupt Request 7

Interrupt Request 6

Interrupt Request 5

Interrupt Request 4

Interrupt Request 3

DMA Acknowledge 2

DMA Terminal Count

Address latch enable

+5V power

14.3MHz clock

Ground

Ground