4 design example, 1 buck design steps, An372 – Cirrus Logic AN372 User Manual

Page 24

AN372

24

AN372REV1

4 Design Example

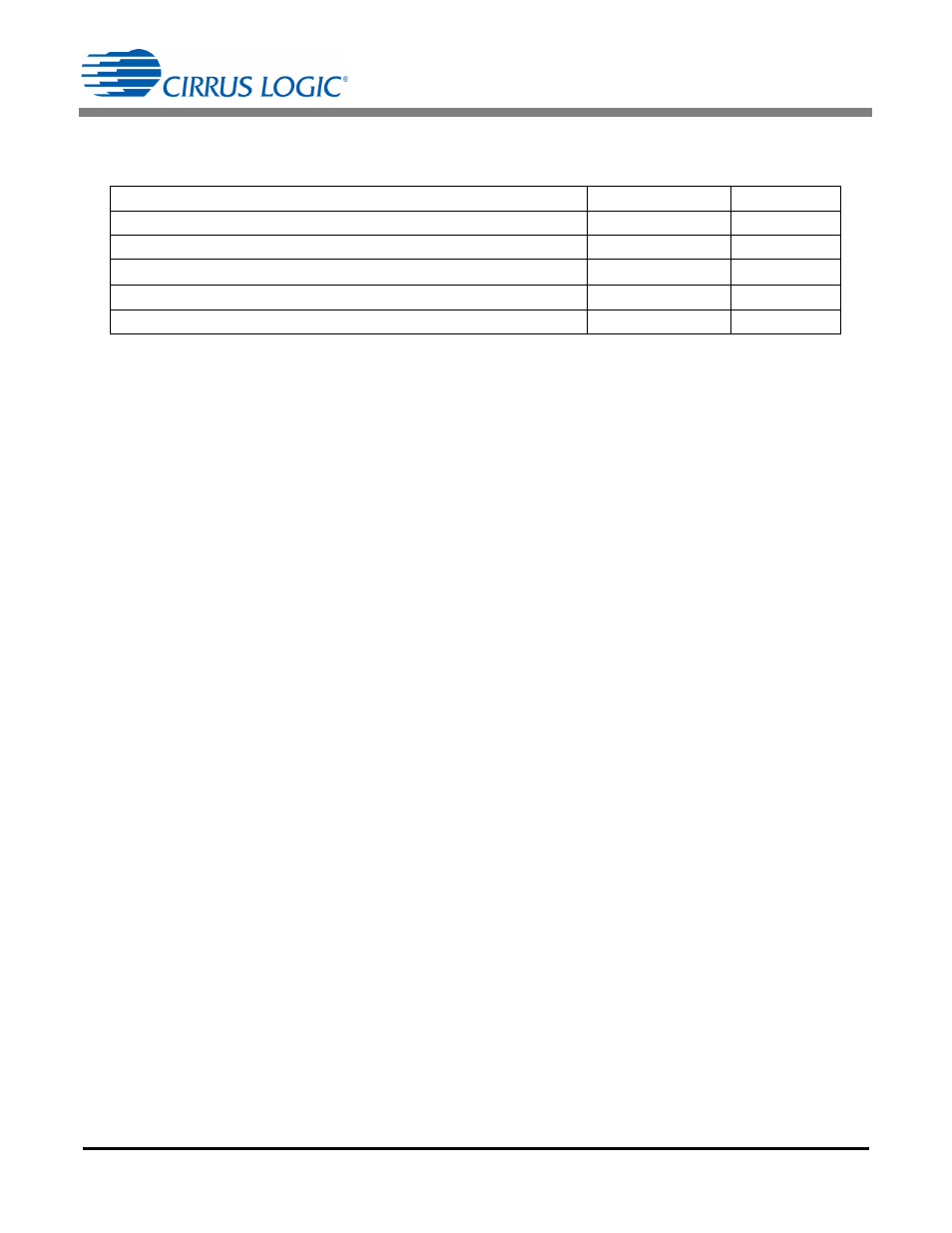

The required operating parameters for the analytical process are outlined in the table below.

4.1 Buck Design Steps

A switching frequency of 125kHz is selected, which corresponds to a switching period TT of 8µs.

Step 1) Choosing a Buck Topology

Normal Buck Circuit Design

A normal buck approach is used to calculate the critical duty cycle

C(min/max)

at minimum output voltage

V

OUT(min)

and maximum boost voltage V

BST(max)

. Solve for

C(min/max)

using Equation 10:

A normal buck approach is used to calculate the critical duty cycle

C(max/min)

at maximum output voltage

V

OUT(max)

and minimum boost voltage V

BST(min)

. Solve for

C(max/min)

using Equation 10:

Assuming an efficiency

= 92% the input power P

IN

required from boost voltage V

BST

is

The current is triangular and flows only during the critical duty cycle

C

which is a fraction of the switching

cycle, the peak current I

PK(FB)

is

where

I

AV

= Average current

Calculate the current at minimum boost voltage V

BST(min)

Calculate time T1 and T2 at maximum boost voltage V

BST(max)

Parameters

Symbol

Value

Output Power

P

OUT

9.6W

AC Line Input Voltage

V

IN

230V

Output Voltage

V

OUT

24V

5%

Load Current

I

OUT

400mA

Maximum Switching Frequency

*

F

sw(max)

125kHz

* Increasing F

SW

reduces the size of the magnetics but increases switching losses in the FET.

C min/max

V

OUT min

V

BST max

---------------------------

=

24V 1.2V

–

405V 40.5V

+

-----------------------------------------

5.1%

=

=

[Eq. 31]

C max/min

V

OUT max

V

BST min

----------------------------

=

24V 1.2V

+

405V 40.5V

–

-----------------------------------------

6.9%

=

=

[Eq. 32]

P

IN

P

OUT

-----------------

=

9.6W

0.92

--------------

10.5W

=

=

[Eq. 33]

I

PK FB

2 I

AV

C

------------------

2 29mA

0.069

--------------------------

=

=

840mA

=

[Eq. 34]

P

IN

V

BST min

--------------------------

10.5W

405V 40.5V

–

-----------------------------------------

=

29mA

=

[Eq. 35]

T1

C min/max

TT

0.051 8

s

408ns

=

=

=

[Eq. 36]

T2

TT T1

–

8

s 408ns

–

7.592

s

=

=

=

[Eq. 37]