Cs8952 – Cirrus Logic CS8952 User Manual

Page 56

CS8952

CrystalLAN™ 100BASE-X and 10BASE-T Transceiver

56

DS206F1

8

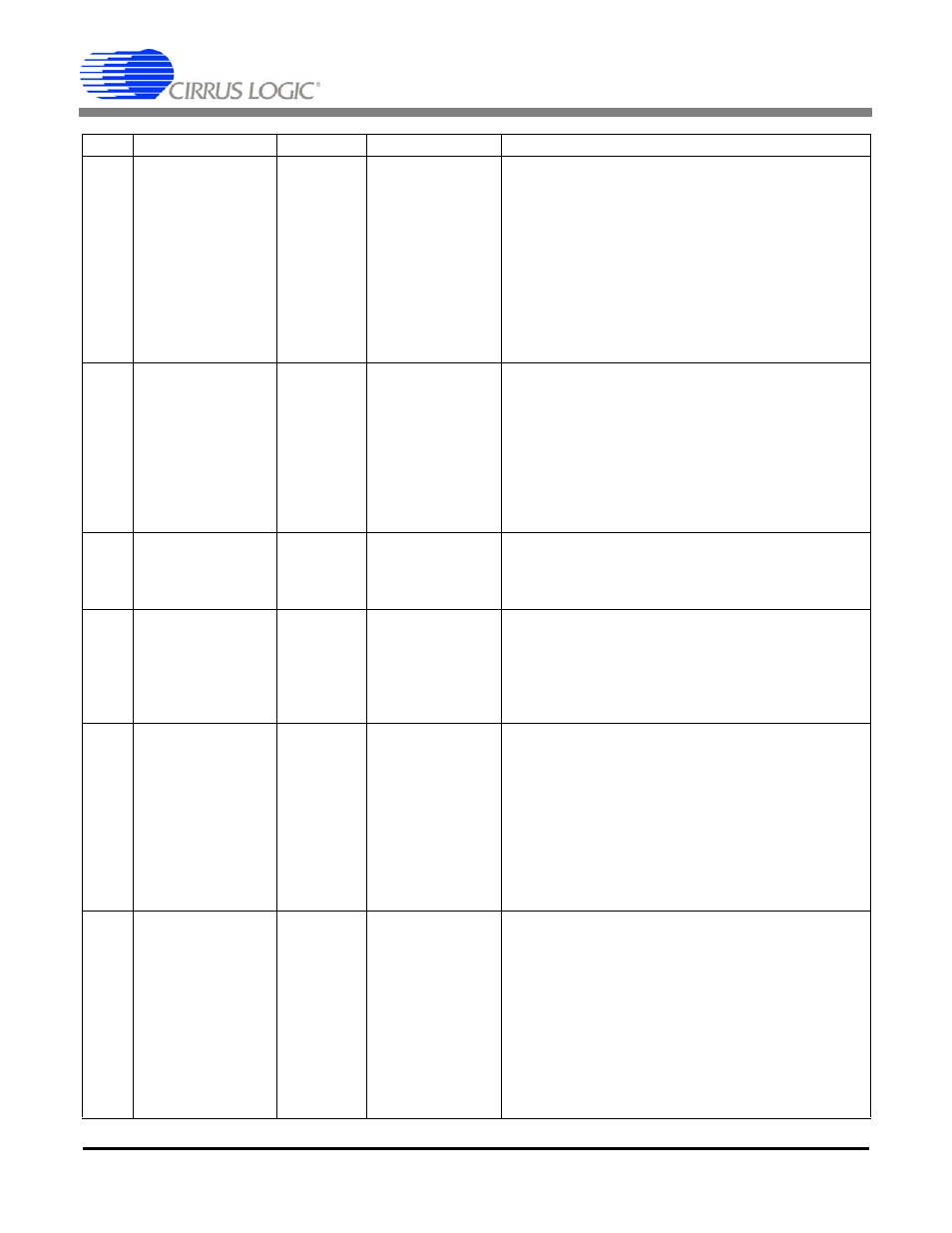

PMD Loopback

Read/Write 0

When set, the scrambled NRZI transmit data is con-

nected directly to the NRZI receive port on the

descrambler. The loopback includes all of the

100BASE-TX functionality except for the MLT-3

encoding/decoding and the analog line-interface

blocks. When clear, the CS8952 is configured for

normal operation.

Note: Setting Remote Loopback and PMD Loopback

simultaneously will cause neither loopback mode to

be entered, and should not be done.

7

Strip Preamble

Read/Write 0

When set this bit causes the 7 bytes of MAC pream-

ble to be stripped off of incoming 100 Mb/s frames.

The data received across the MII will begin with the 1

byte Start of Frame Delimiter (SFD).

Note: This bit is disabled, and writes to this bit are

ignored when the National Compatibility Mode bit of

the 10BASE-T Configuration Register (address 1Ch)

is set.

6

Alternate FDX CRS Read/Write 0

This bit changes the behavior of the CRS pin only in

the full-duplex (FDX) mode of operation. When set,

CRS will be asserted for transmit data only. When

clear, CRS will be asserted only for receive data.

5

Loopback Transmit

Disable

Read/Write 1

This bit controls whether loopback data is transmitted

onto the network. When set, any data transmitted

during PMD or ENDEC loopback mode will NOT be

transmitted onto the network. When clear, data will

be transmitted on the TX+/- pins as well as looped

back onto the MII pins.

4

Code Error Report

Select

Read/Write 0

When set, this bit causes code errors to be reported

by a value of 5h on RXD[3:0] and the assertion of

RX_ER.

When clear, this bit causes code errors to be

reported by a value of 6h on RXD[3:0] and the asser-

tion of RX_ER.

This bit is superseded by the Code Error Report

Enable bit.

3

Premature End

Error Report Select

Read/Write 0

When set, this bit causes premature end errors to be

reported by a value of 4h on RXD[3:0] and the asser-

tion of RX_ER.

When clear, this bit causes premature end errors to

be reported by a value of 6h on RXD[3:0] and the

assertion of RX_ER.

A premature end error is caused by the detection of

two IDLE symbols in the 100 Mb/s receive data

stream prior to the End of Stream Delimiter.

BIT

NAME

TYPE

RESET

DESCRIPTION