3 mii transmit data, 4 mii management interface, 3 mii transmit data 4.4 mii management interface – Cirrus Logic CS8952 User Manual

Page 27: Cs8952

CS8952

CrystalLAN™ 100BASE-X and 10BASE-T Transceiver

27

DS206F1

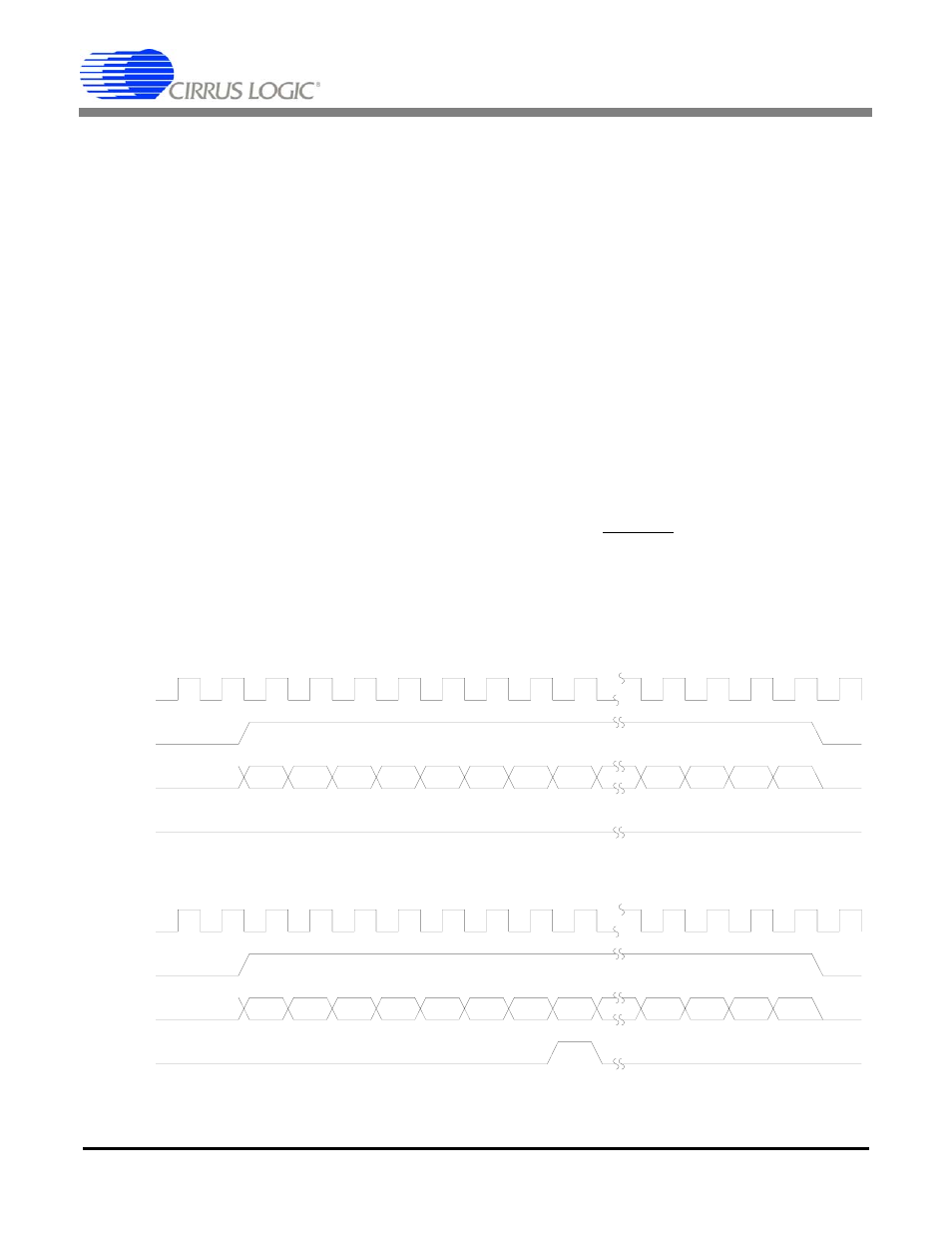

onto RXD[3:0] synchronously with respect to

RX_CLK.

Receive errors are indicated during frame reception

by the assertion of RX_ER. It indicates that an error

was detected somewhere in the frame currently be-

ing transferred across the MII. RX_ER will transi-

tion synchronously with respect to the RX_CLK,

and will be held high for one cycle for each error re-

ceived. It is up to the MAC to ensure that a CRC er-

ror is detected in that frame by the Logical Link

Control. Figure 2 illustrates reception without er-

rors, and Figure 3 illustrates reception with errors.

4.3

MII Transmit Data

TX_EN is used by the MAC to signal to the

CS8952 that valid nibbles of data are being present-

ed across the MII via TXD[3:0]. TX_EN must be

asserted synchronously with the first nibble of pre-

amble, and must remain asserted as long as valid

data is being presented to the MII.

TX_EN must be de-asserted within one TX_CLK

cycle after the last nibble of data (CRC) has been

presented to the CS8952. When TX_EN is not as-

serted, data on TXD[3:0] is ignored.

Transmit errors should be signaled by the MAC by

asserting TX_ER for one or more TX_CLK cycles.

TX_ER must be synchronous with TX_CLK. This

will cause the CS8952 to replace the nibble with a

HALT symbol in the frame being transmitted. This

invalid data will be detected by the receiving PHY

and flagged as a bad frame. Figure 4 illustrates

transmission without errors, and Figure 5 illustrates

transmission with errors.

4.4

MII Management Interface

The CS8952 provides an enhanced IEEE 802.3 MII

Management Interface. The interface consists of

three signals: a bi-directional serial data line

(MDIO), a data clock (MDC), and an optional in-

terrupt signal (MII_IRQ). The Management Inter-

face can be used to access status and control

registers internal to the CS8952. The CS8952 im-

plements an extended set of 16-bit MII registers.

Eight of the registers are defined by the IEEE 802.3

RX_CLK

RX_DV

RXD[3:0]

RX_ER

Preamble/SFD

DATA

Figure 2. Reception without errors

RX_CLK

RX_DV

RXD[3:0]

RX_ER

Preamble/SFD

DATA

XX

DATA

Figure 3. Reception with errors