Cs8952 – Cirrus Logic CS8952 User Manual

Page 53

CS8952

CrystalLAN™ 100BASE-X and 10BASE-T Transceiver

53

DS206F1

9

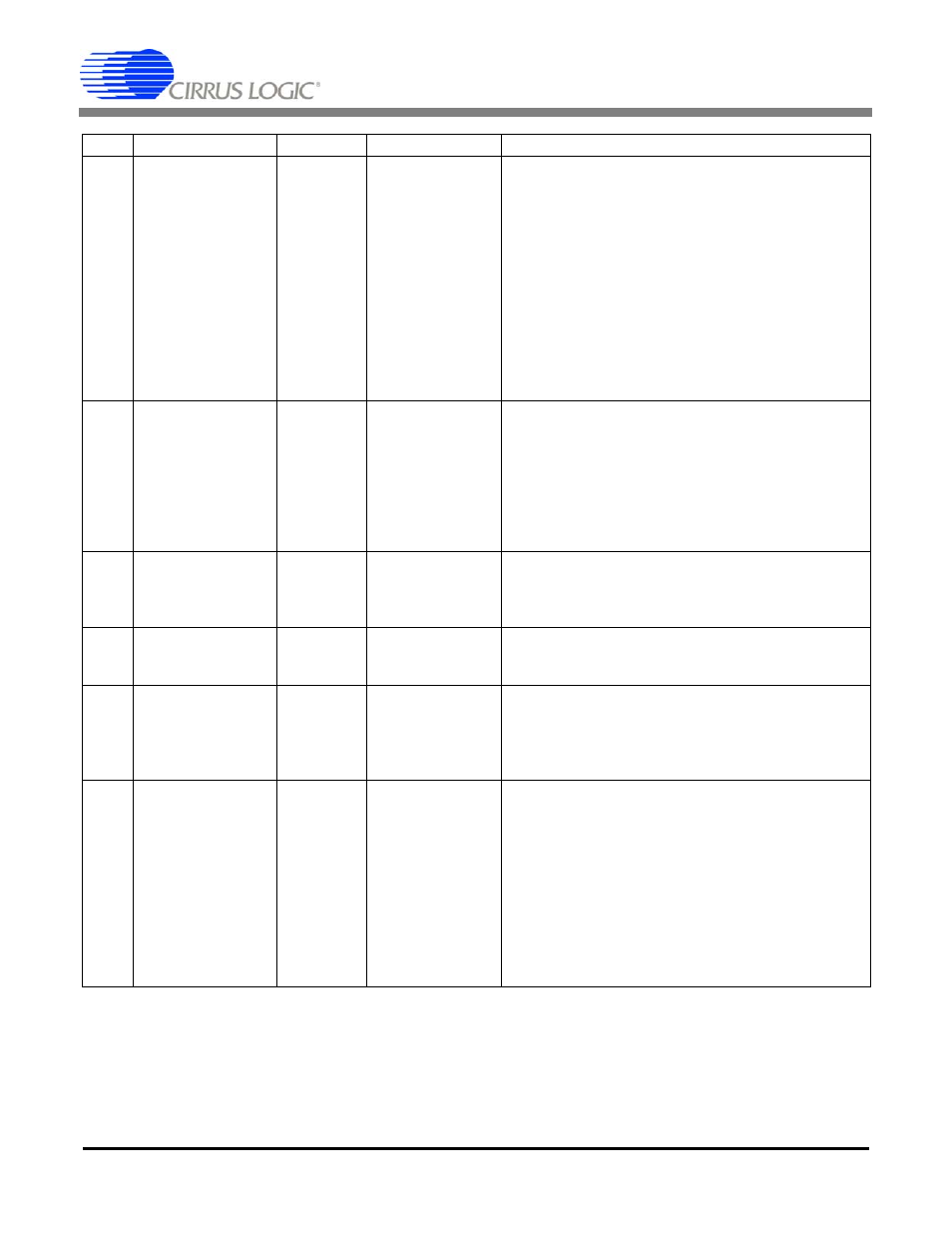

MF Preamble

Enable

Read/Write 0

When set, this bit will force all management frames

(via MDIO, MDC) to be preceded by a 32 bit pream-

ble pattern of contiguous ones to be considered

valid. When cleared, it allows management frames

with or without the preamble pattern. The status of

this register is (inversely) reflected in the MF Pream-

ble bit in the Basic Mode Status Register (address

01h).

Note: This bit is disabled, and writes to this bit are

ignored when the National Compatibility Mode bit of

the 10BASE-T Configuration Register (address 1Ch)

is set.

8

Fast Test

Read/Write 0

When set, internal timers are sped up significantly in

order to facilitate production test. Leave clear for

proper operation.

Note: This bit is disabled, and writes to this bit are

ignored when the National Compatibility Mode bit of

the 10BASE-T Configuration Register (address 1Ch)

is set.

7

CLK25 Disable

Read/Write When TCM pin is

low, reset to 1;

otherwise, reset to

0

Setting this bit will disable (tri-state) the CLK25 out-

put pin, reducing digital noise and power consump-

tion.

6

Enable LT/100

Read/Write 1

When set, normal link status checking is enabled.

When clear, this bit forces the link status to Link OK

(at 100 Mb/s), and will assert the LINK_OK LED.

5

CIM Disable

Read/Write Reset to the logic

inverse of the

value on the

REPEATER pin.

When set, this bit forces the Carrier Integrity Monitor

function to be disabled. When low, the Carrier Integ-

rity Monitor function is enabled, and detection of an

unstable link will disable the receive and transmit

functions.

4

Tx Disable

Read/Write 0

When set, this bit forces the 10 Mb/s and 100 Mb/s

outputs to be inactive. When clear, normal transmis-

sion is enabled.

If Tx Disable is set while a packet is being transmit-

ted, transmission is completed and no subsequent

packets are transmitted until Tx Disable is cleared

again. Also, if Tx Disable is cleared while TX_EN is

high, the transmitter will remain disabled until TX_EN

is deasserted. This prevents fragments from being

transmitted onto the network.

BIT

NAME

TYPE

RESET

DESCRIPTION