Cs8952 – Cirrus Logic CS8952 User Manual

Page 31

CS8952

CrystalLAN™ 100BASE-X and 10BASE-T Transceiver

31

DS206F1

6.1

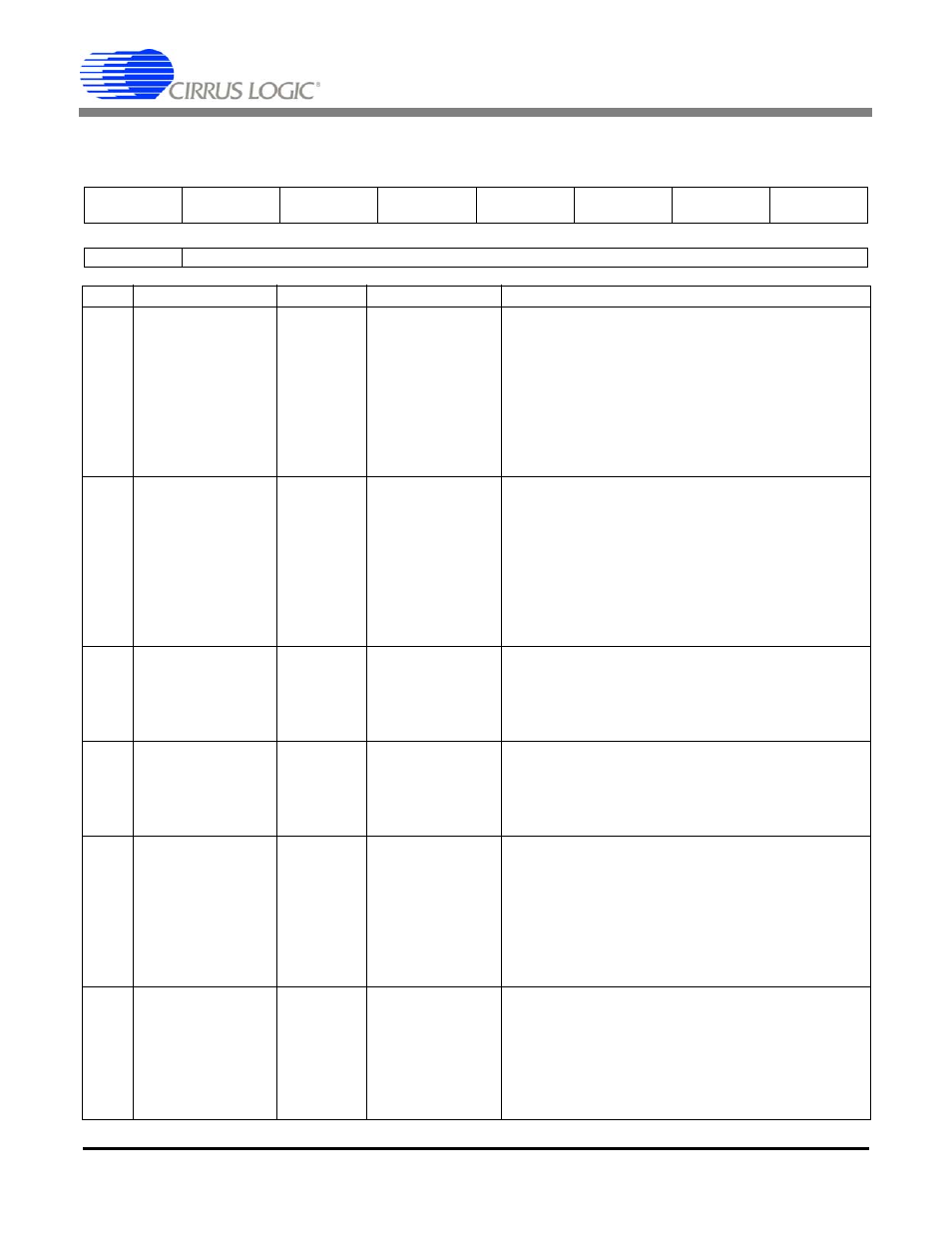

Basic Mode Control Register - Address 00h

15

14

13

12

11

10

9

8

Software

Reset

Loopback

Speed

Selection

Auto-Neg

Enable

Power Down

Isolate

Restart

Auto-Neg

Duplex Mode

7

6

5

4

3

2

1

0

Collision Test

Reserved

BIT

NAME

TYPE

RESET

DESCRIPTION

15

Software Reset

Read/Set

0

Setting this bit performs a chip-wide reset. All status

and control registers are set to their default states,

and the analog circuitry is re-calibrated. This bit is an

Act-Once bit which is cleared once the reset and re-

calibration have completed.

This bit will also be set automatically while the analog

circuitry is reset and re-calibrated during mode

changes.

14

Loopback

Read/Write 0

When set, the CS8952 is placed in a loop back

mode. Any data sent on the transmit data path is

returned on the receive data path. Loopback mode is

entered regardless of whether 10 Mb/s or 100 Mb/s

operation has been configured.

This bit will be set upon the assertion of the LPBK

pin, and will be automatically cleared upon its deas-

sertion.

13

Speed Selection

Read/Write If auto-negotiation

is enabled via the

AN[1:0] pins, reset

to 1; otherwise,

reset to 0

When bit 12 is clear, setting this bit configures the

CS8952 for 100 Mb/s operation. Clearing this bit sets

the configuration at 10 Mb/s. When bit 12 is set, this

bit is ignored.

12

Auto-Neg Enable

Read/Write If auto-negotiation

is enabled via the

AN[1:0] pins, reset

to 1; otherwise,

reset to 0

Setting this bit enables the auto-negotiation process.

When this bit is set, bits 13 and 8 have no affect on

the link configuration. The link configuration is deter-

mined by the auto-negotiation process. Clearing this

bit disables auto-negotiation.

11

Power Down

Read/Write 0

When this bit is set, the CS8952 enters a low power

consumption state. Clearing this bit allows normal

operation.

Note: This bit is disabled, and writes to this bit are

ignored when the National Compatibility Mode bit of

the 10BASE-T Configuration Register (address 1Ch)

is set.

10

Isolate

Read/Write If PHYAD =

00000, reset to 1;

otherwise reset to

the value on the

ISODEF pin

Setting this bit causes the MII data path to be electri-

cally isolated by tri-stating all data outputs (i.e.

TX_CLK, RX_CLK, RX_DV, RX_ER, RXD[3:0], COL,

and CRS). In addition the CS8952 will not respond to

the TXD[3:0], TX_EN, and TX_ER inputs. It will, how-

ever, respond to MDIO and MDC. Clearing this bit

allows normal operation.