10base-t mii receive timing, Cs8952 – Cirrus Logic CS8952 User Manual

Page 12

CS8952

CrystalLAN™ 100BASE-X and 10BASE-T Transceiver

12

DS206F1

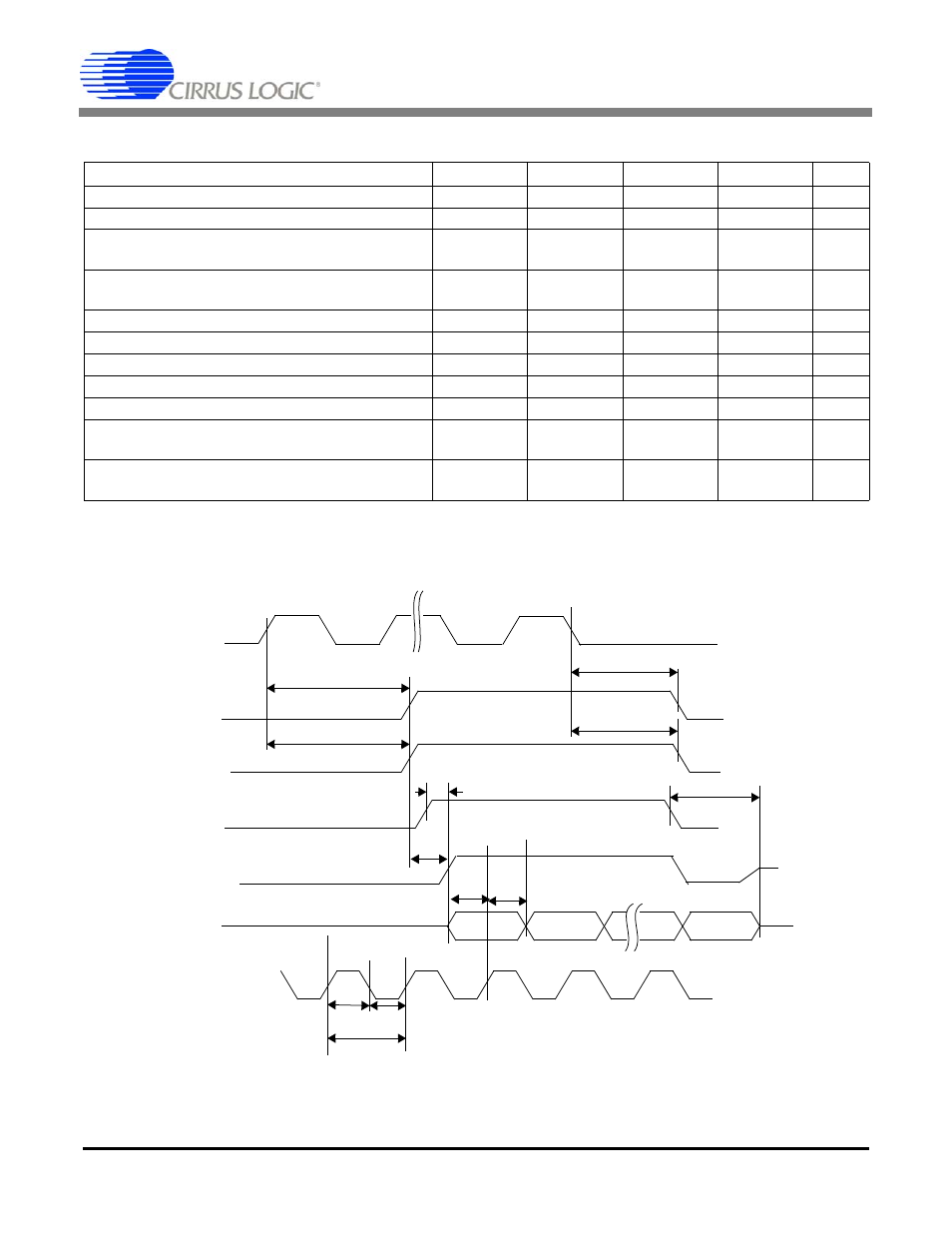

10BASE-T MII RECEIVE TIMING

Parameter

Symbol

Min

Typ

Max

Unit

RX_CLK Period

t

P

-

400

-

ns

RX_CLK Pulse Width

t

WL,

t

WH

-

200

-

ns

RXD[3:0], RX_ER, RX_DV setup to rising edge of

RX_CLK

t

SU

30

-

-

ns

RXD[3:0], RX_ER, RX_DV hold from rising edge

of RX_CLK

t

HD

30

-

-

ns

RX data valid from CRS

t

RLAT

-

8

10

BT

RX+/- preamble to CRS asserted

t

CRS1

-

5

7

BT

RX+/- end of packet to CRS de-asserted

t

CRS2

2.5

3

BT

RX+/- preamble to COL asserted

t

COL1

0

-

7

BT

RX+/- end of packet to COL de-asserted

t

COL2

-

-

3

BT

RX_EN asserted to RX_DV, RXD[3:0], RX_ER

valid

t

EN

-

-

60

ns

RX_EN de-asserted to RX_DV, RXD[3:0]. RX_ER

in high impedance state

t

DIS

-

-

60

ns

RX_CLK

RXD[3:0],

CRS

t

CRS1

t

COL2

t

RLAT

RX_EN

RX+/-

RX_DV

IN

OUT

IN

OUT

OUT

OUT

COL

t

COL1

t

CRS2

t

HD

t

EN

t

DIS

RX_ER

t

WL

t

WH

t

P

t

SU

OUT

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)