Cs8952 – Cirrus Logic CS8952 User Manual

Page 55

CS8952

CrystalLAN™ 100BASE-X and 10BASE-T Transceiver

55

DS206F1

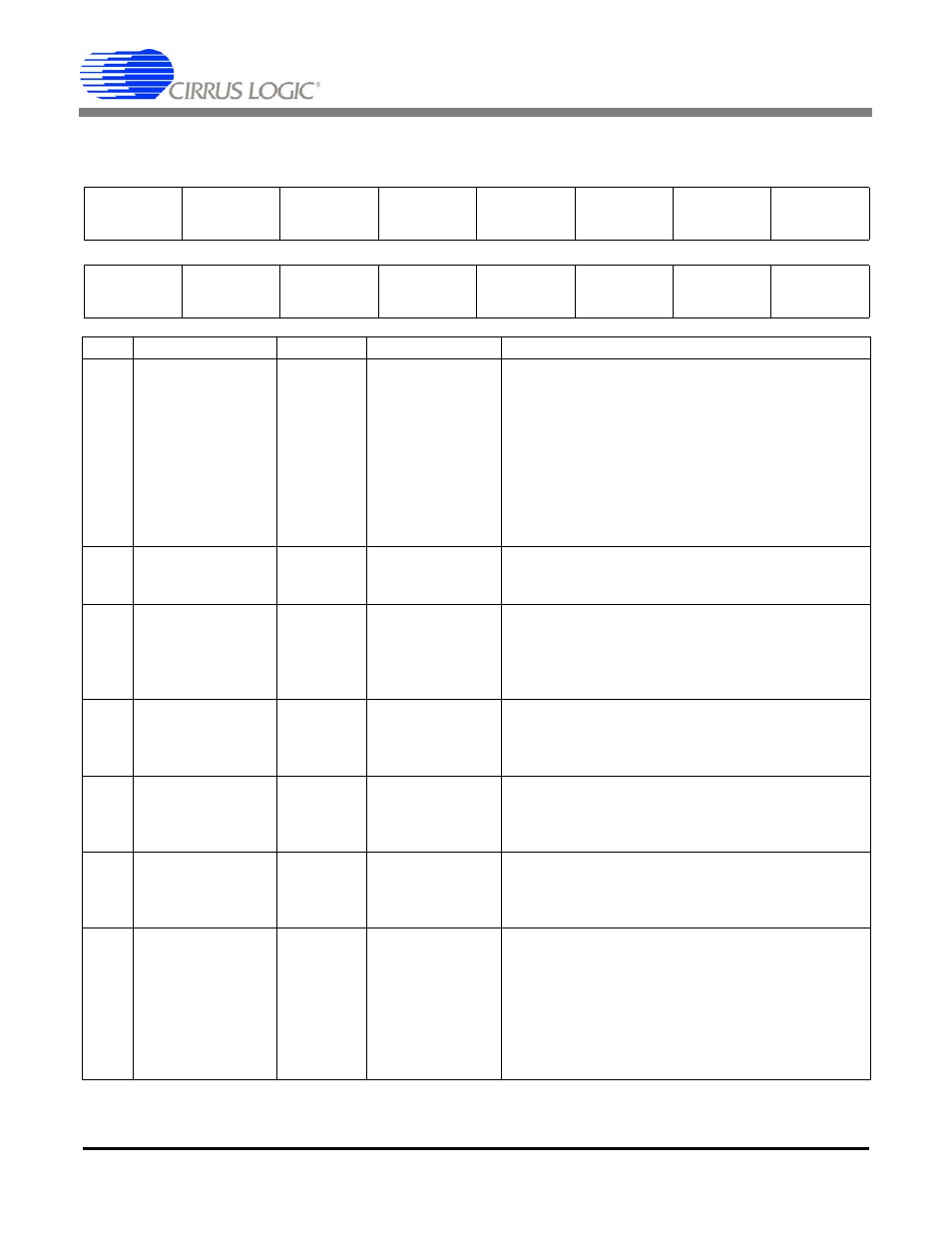

6.17

Loopback, Bypass, and Receiver Error Mask Register - Address 18h

15

14

13

12

11

10

9

8

Bad SSD

Enable

Bypass 4B5B

Bypass

Scrambler

Bypass

Symbol

Alignment

ENDEC

Loopback

FX Drive

Remote

Loopback

PMD

Loopback

7

6

5

4

3

2

1

0

Strip Preamble

Alternate FDX

CRS

Loopback

Transmit

Disable

Code Error

Report Select

Premature End

Error Report

Select

Link Error

Report Enable

Packet Error

Report Enable

Code Error

Report Enable

BIT

NAME

TYPE

RESET

DESCRIPTION

15

Bad SSD Enable

Read/Write 1

When set, this bit enables the reporting of a bad SSD

(False-Carrier event) on the MII. These events will be

reported by setting RX_ER=1, RX_DV=0, and

RXD[3:0]=1110.

If the 4B5B encoders are being bypassed, this event

will be reported by setting RX_DV=0 and

RXD[4:0]=11110. If symbol alignment is bypassed,

the CS8952 does not detect carrier, and thus will not

report bad SSD events.

14

Bypass 4B5B

Read/Write Reset to the value

on the BP4B5B

pin.

When set, this bit causes the receive 5B4B decoder

and the transmit 4B5B encoder to be bypassed.

13

Bypass Scrambler

Read/Write Reset to the value

on the BPSCR

pin.

When set, this bit causes the receive descrambler

and the transmit scrambler blocks to be bypassed,

and the CS8952 accepts NRZI data from an external

100BASE-FX optical module through pins RX_NRZ+

and RX_NRZ-.

12

Bypass Symbol

Alignment

Read/Write Reset to the value

on the BPALIGN

pin.

When set, this bit causes the following functions to

be bypassed: receiver descrambling, symbol align-

ment and decoding, transmit symbol encoding, and

transmit scrambling.

11

ENDEC Loopback

Read/Write 0

When set, the 10BASE-T internal Manchester

encoder output is connected to the decoder input.

When clear, the CS8952 is configured for normal

operation.

10

FX Drive

Read/Write 0

This bit controls the drive strength of the 100BASE-

FX PECL interface drivers. When clear, the drivers

are optimized for a 50

Ω load. When set, the drivers

are optimized for a 150

Ω load.

9

Remote Loopback

Read/Write 0

When set, data received from the link is looped back

at the MII and sent back out to the link. Received

data will be presented on the MII pins. Transmit data

at the MII will be ignored.

Note: Setting Remote Loopback and PMD Loopback

simultaneously will cause neither loopback mode to

be entered, and should not be done.