Figure 16. aui schematic, Figure 17. 10base-2 schematic, Figure 18. pal decode of la[20-23 – Cirrus Logic AN83 User Manual

Page 25: H 17, An83

AN83

AN83REV3

25

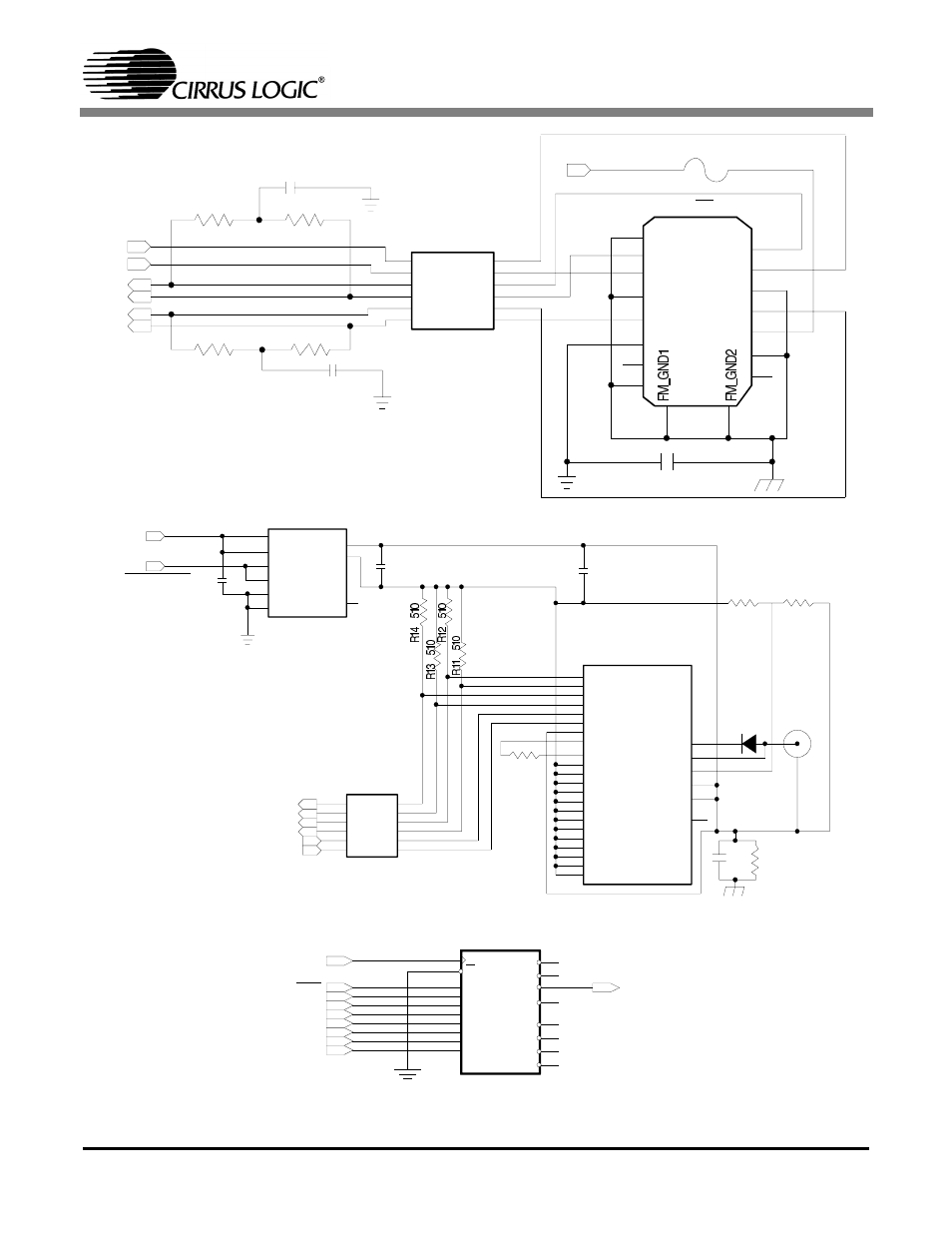

Figure 16. AUI Schematic

Figure 17. 10BASE-2 Schematic

Figure 18. PAL Decode of LA[20-23]

+12V

0.1

µF

BSTATUS/HCI

1

2

4

5

7

8

16

15

13

12

10

9

AUI_XFR_S

T1

I11

I12

I21

I22

I31

I32

O11

O12

O21

O22

O31

O32

DO+

CI-

CI+

DI-

DI+

DO-

14

13

12

4

3

2

TX+

RX-

RX+

CD-

CD+

C18

0.1

µF

1

2

3

22

23

24

+12IN1

+12IN2

EN

EN

-12IN1

-12IN2

SOUT+

SOUT-

12

9

13

NC

U5

DC-DC

CONVERSION

C21

0.1

µF

ISOLATED_GND

-9_V

1082 DO-

1082 DO+

1082 DI-

1082 DI+

1082 CI-

1082 CI+

R10 1K

TX-

HBE

RR+

RR-

VEE5

VEE4

VEE3

VEE2

VEE1

VEE6

VEE9

VEE8

VEE7

VEE10

VEE12

VEE11

VEE13

18

15

19

10

9

8

7

6

5

20

11

23

22

21

25

24

CDS

TX0

RX1

GND1

GND2

NC

1

28

26

16

17

27

CS83C92C_S

U2

CDS

TX0

RX1

D1

1H916

C20

R15 10k

R16 121

J3

BNC_50

1

2

C24

1kV

.01

µF

1M

1/2W

R17

DO-

DO+

CI-

CI+

DI-

DI+

R6

39.2

R8

39.2

Ω R9

39.2

R7

39.2

C14

CI-

CI+

DI-

DI+

0.1

µF

C15

1

2

4

5

7

8

16

15

13

12

10

9

AUI_XFR_S

T2

1

2

3

4

5

6

7

8

CI_A

DO_A

DI_A

CON_AUI15PSUBO

J2

9

10

11

12

13

14

15

16

17

CI_B

DO_B

DI_B

0.1

µF

C27

+12V

F1

VP_+12V

I11

I12

I21

I22

I31

I32

O11

O12

O21

O22

O31

O32

0.1

µF

1

11

2

3

4

5

6

7

8

9

CLK

G

10

11

12

13

14

15

16

17

I/00

I/01

I/02

I/03

12

13

18

19

14

15

16

17

00

01

02

03

CHIPSEL_B (CS8900 Pin7)

PAL16R4

ELCS

EEDOUT

BALE

LA23

LA22

LA21

LA20

RESET

EE_SK

(CS8900 Pin2)

CS8900 Pin5)

(ISA B28)

(ISA C02)

(ISA C03)

(ISA C04)

(ISA C05)

(ISA B02)

(CS8900 Pin 4)