An83 – Cirrus Logic AN83 User Manual

Page 13

AN83

AN83REV3

13

LINK

ACTIVITY

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

nMWE

nMOE

A1

A2

A3

nCS2

CS8900_RST

D[15:0]

A[3:1]

CS8900_RST

nURESET

EINT3

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

C62

560pF

R97

100K

U21

CS8900A

93

37

38

39

40

41

42

43

44

45

46

47

48

50

51

52

53

54

58

59

60

65

66

67

68

71

72

73

74

27

26

25

24

21

20

19

18

7

28

29

62

61

49

36

63

75

77

76

2

3

4

5

6

97

98

99

78

100

84

83

82

81

80

79

92

91

88

87

32

31

30

35

34

33

64

15

13

11

16

14

12

17

9

22

56

69

8

10

23

55

57

70

1

89

86

94

96

90

85

95

RES

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

SA19

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

CHIPSEL

MEMW

MEMR

IOW

IOR

REFRESH

SBHE

AEN

RESET

SLEEP

TESTSEL

ELCS

EECS

EESK

EEDATAOUT

EEDATAIN

XTLI

XTLO

LED0/HC0

BSTATUS/HC1

LANLED

DO-

DO+

CI-

CI+

DI-

DI+

RXD-

RXD+

TXD-

TXD+

INTRQ0

INTRQ1

INTRQ2

INTRQ3

MEMCS16

IOCS16

IOCHRDY

DMARQ0

DMARQ1

DMARQ2

DMACK0

DMACK2

DMACK3

CSOUT

VCC

VCC

VCC

VCC

GND

GND

GND

GND

GND

GND

AVSS0

AVSS1

AVSS2

AVSS3

AVSS4

AVDD1

AVDD2

AVDD3

R94

8R

R95

8R

R96

4K99 1%

X3

20MHz

R91

4K7

R89

390R

C89

100nF

C90

100nF

R93

100R

D7

LED

2

1

C93

100nF

C92

100nF

C94

100nF

R90

390R

D6

LED

2

1

C88

100nF

U30A

74LVX04

1

2

C91

100nF

D[15:0]

A[3:1]

nMWE

nMOE

nCS2

nURESET

RxD-

RxD+

TxD-

TxD+

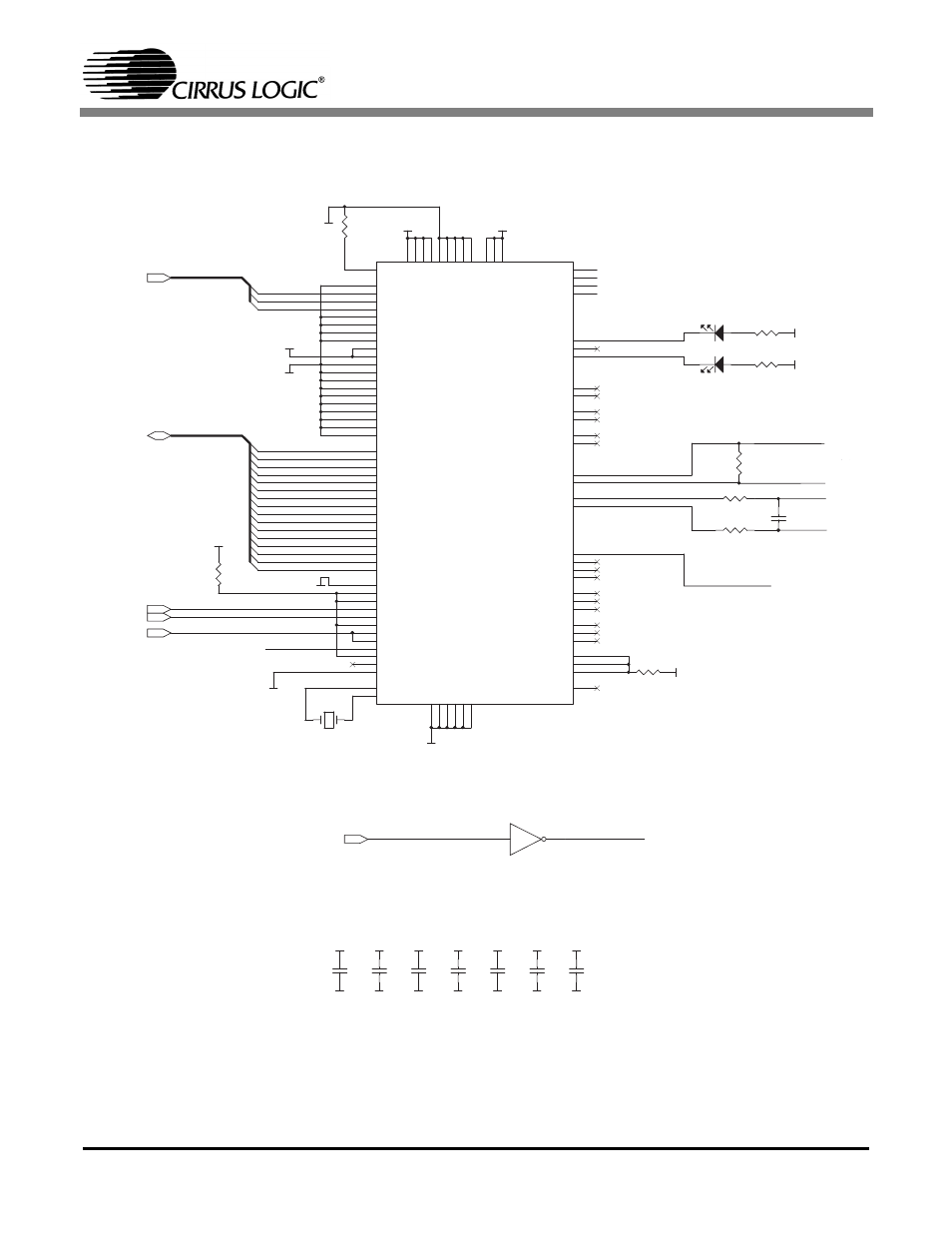

Figure 4. CS8900A Interface to Cirrus Logic CL-PS7211