Durati, 18 voltage sag level register ( vsag, Level – Cirrus Logic CS5461A User Manual

Page 31: Cs5461a, 15 pulsewidth register ( pw ), 16 e3 pulse width register ( pulsewidth, 17 voltage sag duration register ( vsag

CS5461A

DS661F3

31

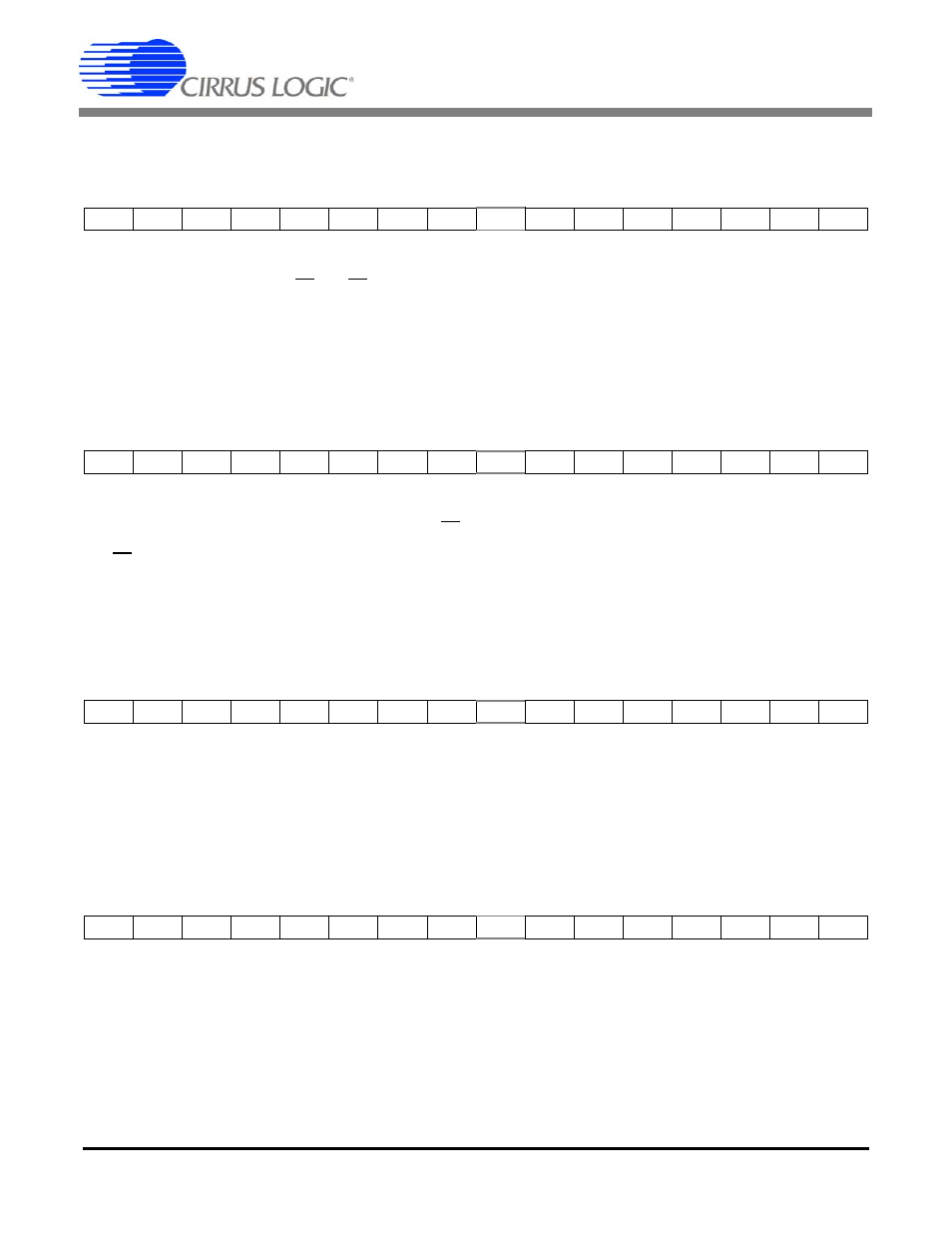

6.15 Pulsewidth Register ( PW )

Address: 21

Default = 0x000200 = 512 sample periods

PW sets the pulsewidth of E1 and E2 pulses in Alternate Pulse and Mechanical Counter format. The width is a

function of number of sample periods. The default corresponds to a pulsewidth of

512 samples/[(MCLK/K)/1024] = 128 msec with MCLK = 4.096 MHz and K = 1. The value is represented in un-

signed notation.

6.16 E3 Pulse Width Register ( PulseWidth

)

Address: 22

Default = 0x000000 = Hardware-generated pulse width (up to 125

s)

The PulseWidth register sets the pulse width of E3 pulses in units of 1/OWR.

E3 pulse width =

The range of this register is from 1 to 8388607.

6.17 Voltage Sag Duration Register ( VSAG

Duration

)

Address: 23

Default = 0x000000

Voltage Sag Duration (VSAG

Duration

)

defines the number of instantaneous voltage measurements utilized to de-

termine a voltage level sag event (VSAG

LEVEL

). Setting this register to zero will disable Voltage Sag-detect. The

value is represented in unsigned notation.

6.18 Voltage Sag Level Register ( VSAG

Level

)

Address: 24

Default = 0x000000

Voltage Sag Level (VSAG

Level

) defines the voltage level that the magnitude of input samples, averaged over the

sag duration, must fall below in order to register a sag condition. This value is represented in unsigned notation

and in the range of 0

VSAG

Level

1.0, with the binary point to the right of the MSB.

MSB

LSB

2

23

2

22

2

21

2

20

2

19

2

18

2

17

2

16

.....

2

6

2

5

2

4

2

3

2

2

2

1

2

0

MSB

LSB

0

2

22

2

21

2

20

2

19

2

18

2

17

2

16

.....

2

6

2

5

2

4

2

3

2

2

2

1

2

0

MSB

LSB

0

2

22

2

21

2

20

2

19

2

18

2

17

2

16

.....

2

6

2

5

2

4

2

3

2

2

2

1

2

0

PulseWidth

MCLK

K

1024

---------------------------------------------

MSB

LSB

0

2

-1

2

-2

2

-3

2

-4

2

-5

2

-6

2

-7

.....

2

-17

2

-18

2

-19

2

-20

2

-21

2

-22

2

-23