Cirrus Logic CS4341A User Manual

Features, Description, 101 db dynamic range

1

Copyright

© Cirrus Logic, Inc. 2004

(All Rights Reserved)

Cirrus Logic, Inc.

http://www.cirrus.com

CS4341A

24-Bit, 192 kHz Stereo DAC with Volume Control

Features

z

101 dB Dynamic Range

z

-91 dB THD+N

z

+3.3 V or +5 V Power Supply

z

50 mW with 3.3 V supply

z

Low Clock Jitter Sensitivity

z

Filtered Line-level Outputs

z

On-Chip Digital De-emphasis for 32, 44.1,

and 48 kHz

z

ATAPI Mixing

z

Digital Volume Control with Soft Ramp

– 94 dB Attenuation

– 1 dB Step Size

– Zero Crossing Click-Free Transitions

z

Up to 200-kHz Sample Rates

z

Automatic Mode Detection for Sample Rates

between 4 and 200 kHz

z

Pin Compatible with the CS4341

Description

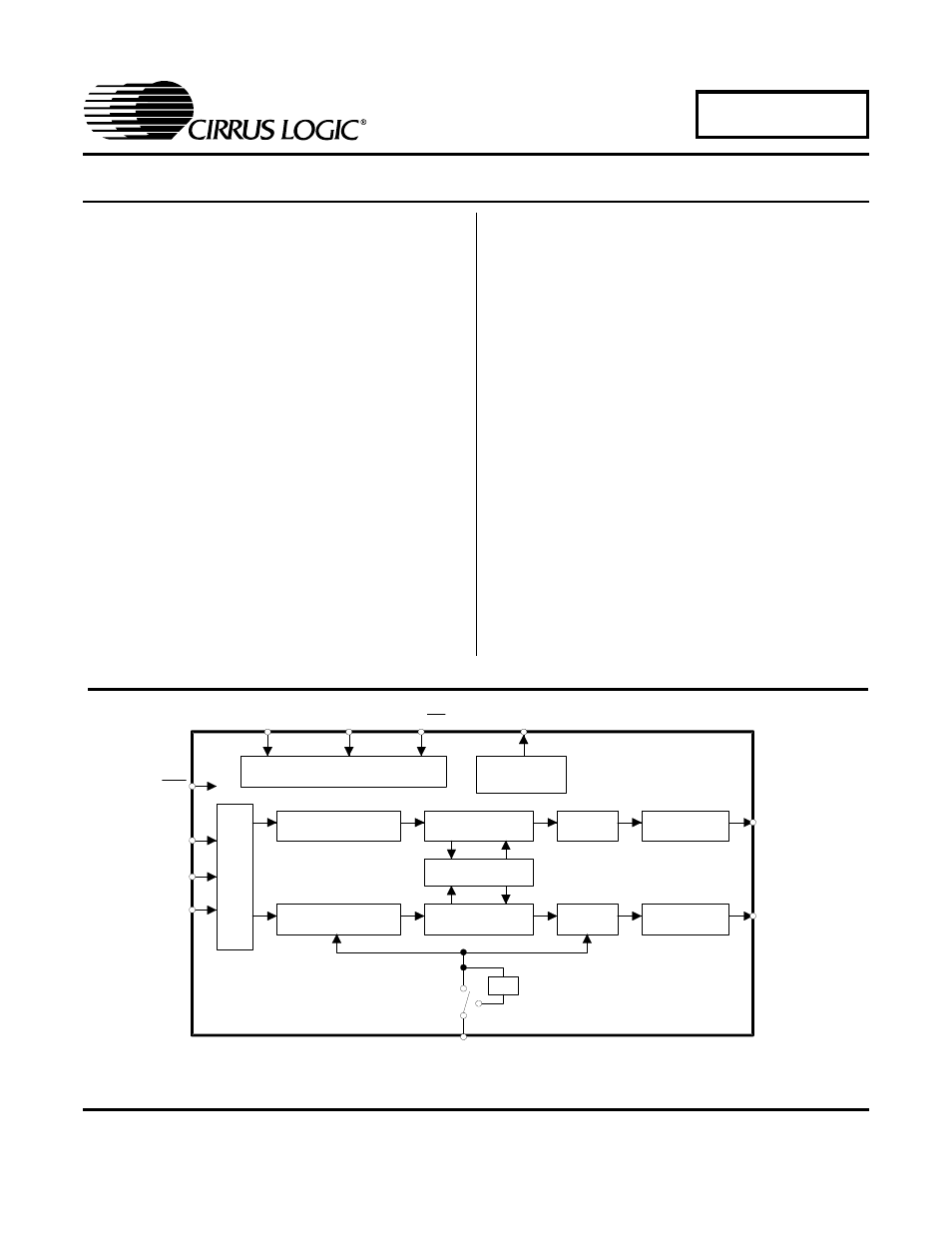

The CS4341A is a complete stereo digital-to-analog sys-

tem including digital interpolation, fourth-order delta-

sigma digital-to-analog conversion, digital de-emphasis,

volume control, channel mixing and analog filtering. The

advantages of this architecture include: ideal differential

linearity, no distortion mechanisms due to resistor

matching errors, no linearity drift over time and tempera-

ture and a high tolerance to clock jitter.

The CS4341A accepts data at all standard audio sample

rates up to 192 kHz, consumes very little power, oper-

ates over a wide power supply range and is pin

compatible with the CS4341, as described in section 3.1.

These features are ideal for DVD audio players.

ORDERING INFORMATION

CS4341A-KS

16-pin SOIC, -10 to 70 °C

CS4341A-KSZ, Lead Free 16-pin SOIC, -10 to 70 °C

CDB4341A

Evaluation Board

Volume Control

Interpolation Filter

∆ Σ

DAC

Analog Filter

Control Port

Interface

Volume Control

Interpolation Filter

Analog Filter

Se

ri

a

l Au

d

io

In

te

rf

a

c

e

SCL/CCLK

M UTEC

AD0/CS

AO UTA

AO UTB

RST

LRCK

SDIN

MCLK

SDA/CDIN

∆ Σ

DAC

External

Mute Control

SCLK

Mixer

÷2

JUL ‘04

DS582F2

Document Outline

- CS4341A

- 1. PIN DESCRIPTION

- 2. Typical Connection Diagram

- 3. Applications

- 3.1 Upgrading from the CS4341 to the CS4341A

- 3.2 Sample Rate Range/Operational Mode Detect

- 3.3 System Clocking

- 3.4 Digital Interface Format

- 3.5 De-Emphasis Control

- 3.6 Recommended Power-up Sequence

- 3.7 Popguard® Transient Control

- 3.8 Grounding and Power Supply Arrangements

- 3.9 Control Port Interface

- 3.10 Memory Address Pointer (MAP)

- 4. Register qUICK rEFERENCE

- 5. Register Description

- 6. Characteristics and Specifications

- Specified Operating Conditions

- Absolute Maximum Ratings

- ANALOG CHARACTERISTICS (CS4341A-kS)

- combined interpolation & on-chip analog Filter response

- Figure 10. Single-Speed Stopband Rejection

- Figure 11. Single-Speed Transition Band

- Figure 12. Single-Speed Transition Band (Detail)

- Figure 13. Single-Speed Passband Ripple

- Figure 14. Double-Speed Stopband Rejection

- Figure 15. Double-Speed Transition Band

- Figure 16. Double-Speed Transition Band (Detail)

- Figure 17. Double-Speed Passband Ripple

- SWITCHING SPECIFICATIONS - SERIAL AUDIO INTERFACE

- SWITCHING specifications - CONTROL PORT interface

- SWITCHING specifications - CONTROL PORT INTERFACE

- dC Electrical characteristics

- DIGITAL Input characteristics

- DIGITAL InTERFACE specifications

- 7. PARAMETER DEFINITIONS

- 8. References

- 9. PACKAGE DIMENSIONS