4 spi mode, 4a spi write, Figure 7. control port timing, spi mode – Cirrus Logic CS4341A User Manual

Page 14: Figure 8, Control port timing, spi mode, Cs4341a

CS4341A

14

DS582F2

3.9.4

SPI Mode

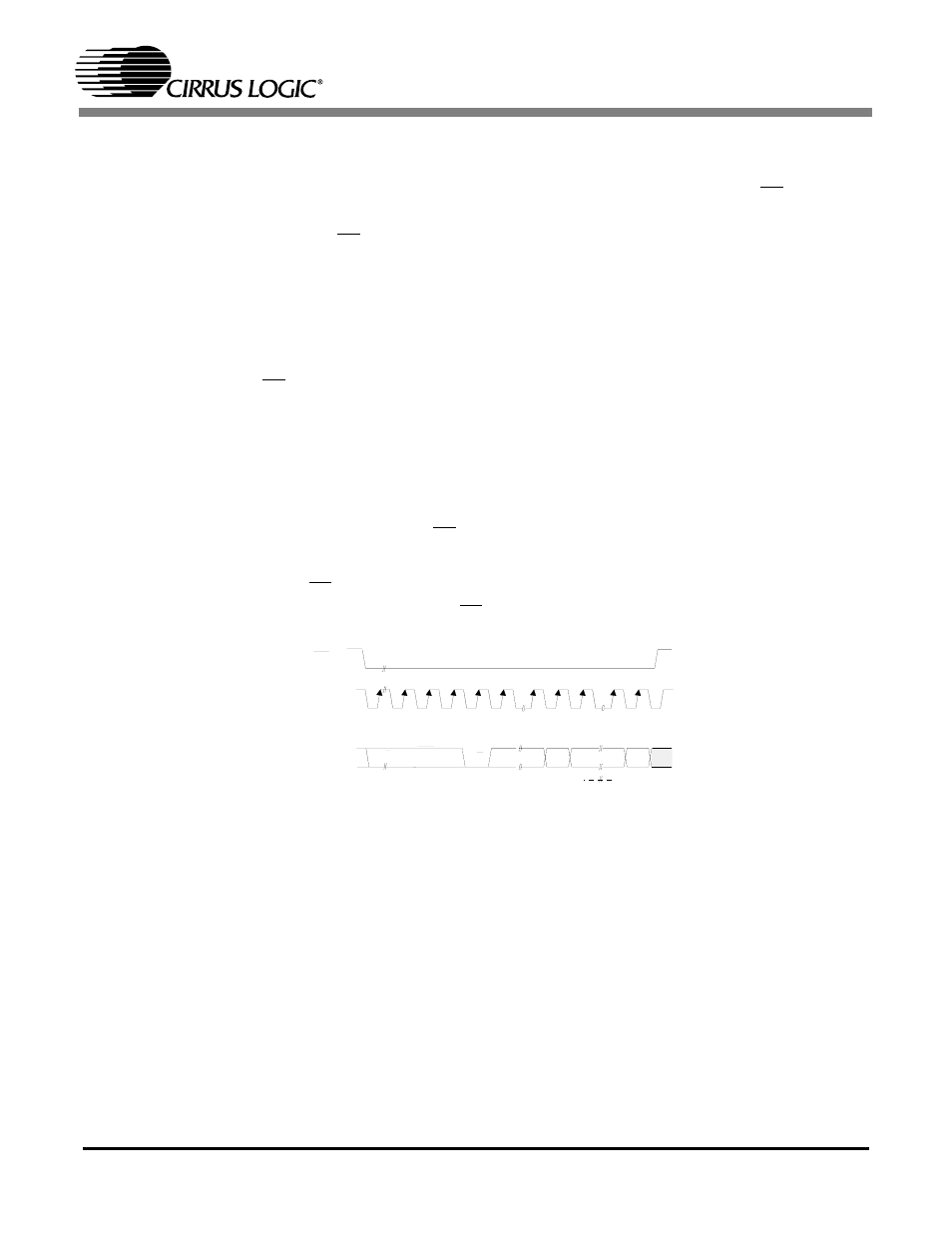

In SPI mode, data is clocked into the serial control data line, CDIN, by the serial control port clock,

CCLK (see Figure 7 for the clock to data relationship). There is no AD0 pin. Pin CS is the chip

select signal and is used to control SPI writes to the control port. When the device detects a high to

low transition on the AD0/CS pin after power-up, SPI mode will be selected. All signals are inputs

and data is clocked in on the rising edge of CCLK.

3.9.4a

SPI Write

To write to the device, follow the procedure below while adhering to the control port

Switching Specifications in section 6.

1) Bring CS low.

2) The address byte on the CDIN pin must then be 00100000.

3) Write to the memory address pointer, MAP. This byte points to the register to be written.

4) Write the desired data to the register pointed to by the MAP.

5) If the INCR bit (see section 3.9.2) is set to 1, repeat the previous step until all the desired

registers are written, then bring CS high.

6) If the INCR bit is set to 0 and further SPI writes to other registers are desired, it is nec-

essary to bring CS high, and follow the procedure detailed from step 1. If no further writes

to other registers are desired, bring CS high.

M A P

MSB

L S B

DATA

b yte 1

byte n

R/W

M A P = M e m ory A d d res s P oin te r

ADDRESS

C H IP

C D IN

C C L K

CS

0 0 1 0 0 0 0

Figure 7. Control Port Timing, SPI mode