Cs4341a – Cirrus Logic CS4341A User Manual

Page 18

CS4341A

18

DS582F2

5.2.1 AUTO-MUTE (AMUTE)

BIT 7

Default = 1

0 - Disabled

1 - Enabled

Function:

The Digital-to-Analog converter output will mute following the reception of 8192 consecutive audio

samples of static 0 or -1. A single sample of non-zero data will release the mute. Detection and mut-

ing is done independently for each channel. The quiescent voltage on the output will be retained and

the Mute Control pin will go active during the mute period. The muting function is affected, similiar to

volume control changes, by the Soft and Zero Cross bits in the Transition and Mixing Control (address

02h) register.

5.2.2 DIGITAL INTERFACE FORMAT (DIF)

BIT 4-6

Default = 000 - Format 0 (I

2

S, up to 24-bit data)

Function:

The required relationship between the Left/Right clock, serial clock and serial data is defined by the

Digital Interface Format and the options are detailed in Figures 2-4.

5.2.3 DE-EMPHASIS CONTROL ( DEM[1:0] )

BIT 2-3

Default = 00

00 - Disabled

01 - 44.1 kHz

10 - 48 kHz

11 - 32 kHz

Function:

Implementation of the standard 15

µs/50µs digital de-emphasis filter response, Figure 5, requires re-

configuration of the digital filter to maintain the proper filter response for 32, 44.1 or 48 kHz sample

rates.

NOTE: De-emphasis is only available in Single-Speed Mode.

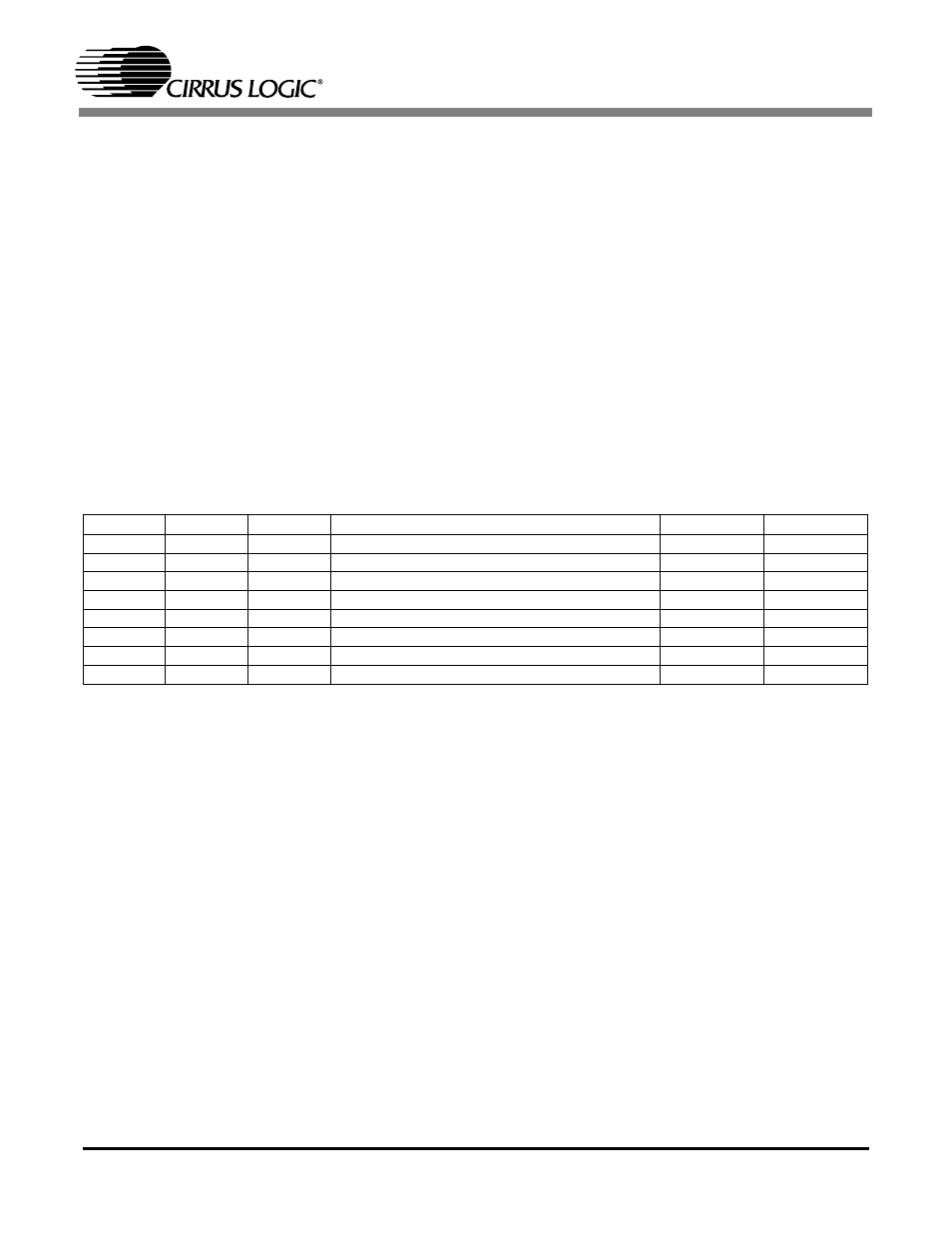

DIF2

DIF1

DIF0

DESCRIPTION

Format

FIGURE

0

0

0

I

2

S, up to 24-bit data

1

0

0

1

Identical to Format 1

1

0

1

0

Left Justified, up to 24-bit data,

2

0

1

1

Right Justified, 24-bit data

3

1

0

0

Right Justified, 20-bit data

4

1

0

1

Right Justified, 16-bit data

5

1

1

0

Right Justified, 18-bit data

6

1

1

1

Identical to Format 1

1

Table 6. Digital Interface Format