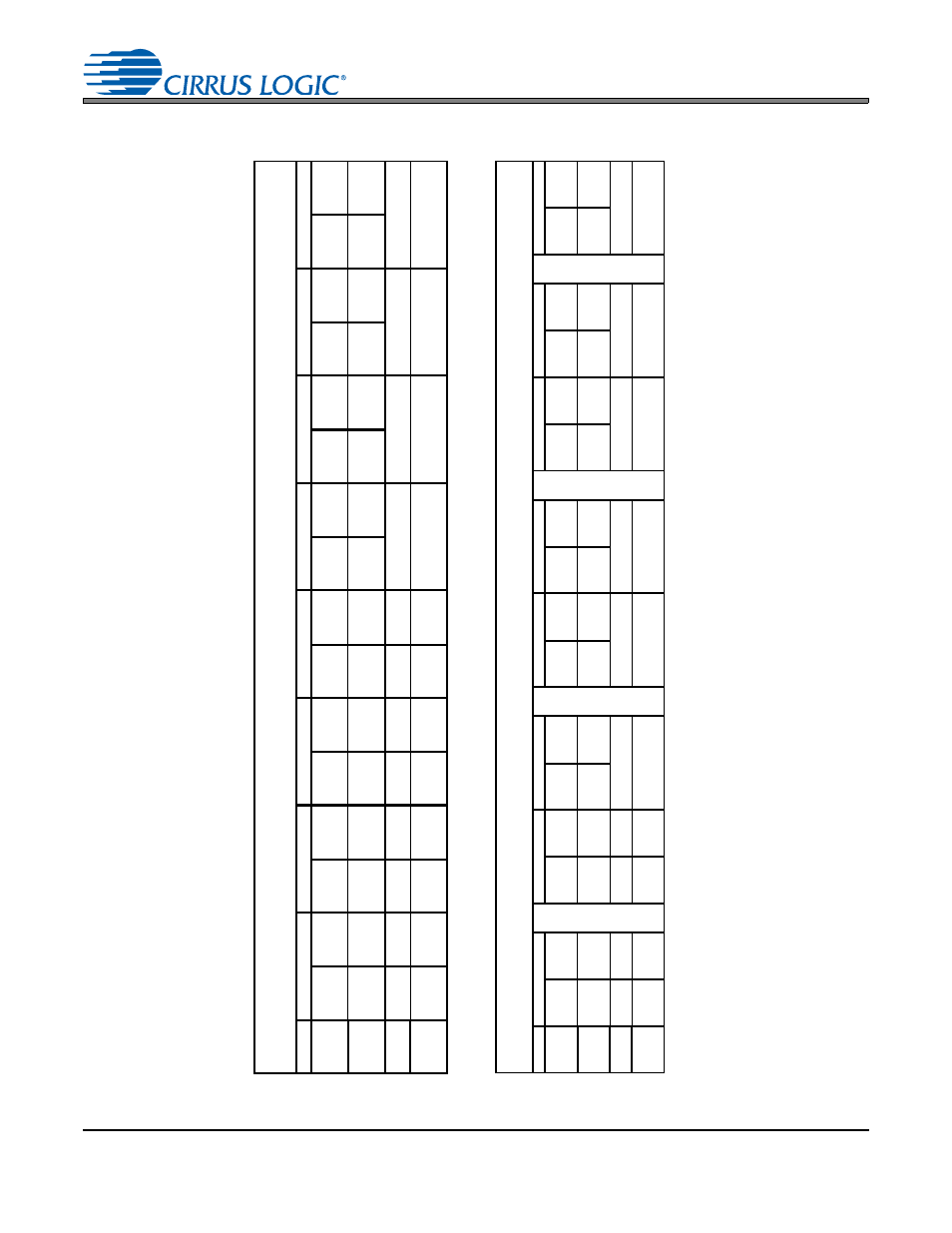

Figure 16, Cs4244 – Cirrus Logic CS4244 User Manual

Page 29

DS900F1

29

CS4244

SDIN

1

In

pu

t Dat

a

1.

1

[31:

8]

x

[7:

0]

In

pu

t D

ata

1.

2

[3

1:

8]

x

[7

:0]

In

pu

t D

a

ta

1

.3

[3

1:

8]

x

[7

:0]

Inp

ut

Da

ta

1

.4

[3

1:

8]

x

[7

:0

]

Inp

u

t Da

ta

1.

5

[3

1:8

]

x

[7

:0

]

In

pu

t Da

ta

1.

6

[3

1:

8]

x

[7

:0

]

In

pu

t Da

ta

1.7

[3

1:

8]

x

[7

:0

]

In

pu

t D

ata

1.8

[3

1:

8]

x

[7

:0

]

SDIN

2

In

pu

t Dat

a

2.

1

[31:

8]

x

[7:

0]

In

pu

t D

ata

2.

2

[3

1:

8]

x

[7

:0]

In

pu

t D

a

ta

2

.3

[3

1:

8]

x[

7:0

]

Inp

ut

Da

ta

2

.4

[3

1:

8]

x

[7

:0

]

Inp

u

t Da

ta

2

.5

[3

1:8

]

x

[7

:0

]

In

pu

t Da

ta

2

.6

[3

1:

8]

x[7:

0]

In

pu

t Da

ta

2.7

[3

1:

8]

x[7

:0]

In

pu

t D

ata

2.8

[3

1:

8]

x[7

:0]

SDO

U

T

1

A

DC1

Da

ta

[31

:8

]

0

's

[7:

0]

ADC2

Da

ta

[3

1:

8]

0

's

[7

:0]

ADC3

Da

ta

[3

1:

8]

0

's

[7

:0]

ADC4

Data

[3

1:

8]

0

's

[7

:0

]

SDO

U

T

1

wi

th

S

ide

ch

ain

A

DC1

Da

ta

[31

:8

]

0

's

[7:

0]

ADC2

Da

ta

[3

1:

8]

0

's

[7

:0]

ADC3

Da

ta

[3

1:

8]

0

's

[7

:0]

ADC4

Da

ta

[3

1:

8]

0

's

[7

:0

]

M

C

L

K

=

12

.2

88

/2

4.5

76

M

Hz

F

S

/L

RCK =

4

8/

96

kHz

S

C

LK =

1

2.

28

8/2

4.

57

6M

Hz

S

lot

1 [

3

1:

0]

S

lot

2 [

3

1:

0]

S

lot

3 [

31:

0]

S

lo

t

4 [3

1:

0]

S

lo

t

5 [3

1:

0]

S

lo

t 6

[

31:

0]

S

lo

t 7

[

3

1:

0]

S

lot

8 [

3

1:

0]

0's

[3

1:

0]

0

's

[3

1:

0]

0

's

[3

1:

0]

0

's

[3

1:

0]

Ou

tpu

t

Data

(S

DIN

2 S

lot

1)

Ou

tp

ut

Dat

a

(SDI

N2 Slo

t 2

)

Ou

tp

ut

Dat

a

(SDI

N2 Slo

t 3

)

Ou

tp

ut

Da

ta

(S

DI

N

2

S

lot

4)

SD

IN

1

In

put D

a

ta

1.

1

[31

:8]

x

[7:0

]

Input Dat

a

1.4

[3

1:8]

x

[7

:0]

In

put D

a

ta

1.

5

[31

:8]

x

[7:

0

]

Input

Dat

a

1.8

[31:8]

x

[7

:0

]

Input D

a

ta

1.

9

[31

:8]

x

[7:

0

]

Input

Da

ta

1.12

[31:8]

x

[7

:0

]

Input D

a

ta

1.

13

[3

1:8]

x

[7

:0]

Inpu

t Da

ta

1.16

[31:8]

x

[7:0]

SD

IN

2

In

put D

a

ta

2.

1

[31

:8]

x

[7:0

]

Input Dat

a

2.4

[3

1:8]

x

[7

:0]

In

put D

a

ta

2.

5

[31

:8]

x

[7:

0

]

Input

Dat

a

2.8

[31:8]

x

[7

:0

]

Input D

a

ta

2.

9

[31

:8]

x

[7:

0

]

Input

Da

ta

2.12

[31:8]

x

[7

:0

]

Input D

a

ta

2.

13

[3

1:8]

x

[7

:0]

Inpu

t Da

ta

2.16

[31:8]

x

[7:0]

SD

O

U

T1

A

D

C1

Da

ta

[31

:8]

0'

s

[7:0

]

A

DC4

Da

ta

[3

1:8]

0'

s

[7

:0]

SD

O

U

T1

wi

th

Sid

ech

ain

A

D

C1

Da

ta

[31

:8]

0'

s

[7:0

]

A

DC4

Da

ta

[3

1:8]

0'

s

[7

:0]

MC

L

K

= 24

.576M

Hz

F

S

/L

R

C

K

= 48

kHz

0'

s

[31

:0]

O

u

tput

Data

(S

DI

N

2

S

lo

t

1)

SC

L

K

= 24

.576M

Hz

S

lo

t 1

[3

1:

0]

…

→

…

Slo

t

4 [

31:

0]

Sl

o

t 5

[3

1:

0]

…

→

…

Slo

t

8 [

31:

0]

S

lo

t 9

[3

1:

0]

Sl

o

t 1

3

[

31:

0]

…

→

…

Slo

t 16

[31:

0]

0's

[31:0]

0'

s

[31:0

]

0's

[31:0]

0'

s

[31:

0]

0's

[31:0

]

…

→

…

Slo

t 12

[31:

0]

Outp

ut D

a

ta

(S

DI

N2

S

lot

1

2

)

Outpu

t D

a

ta

(S

DI

N2

S

lo

t 4

)

O

u

tput

Dat

a

(S

DI

N

2 S

lo

t 5)

Outp

ut D

a

ta

(S

DI

N2

S

lot

8

)

O

u

tpu

t Da

ta

(S

D

IN2

Sl

ot

9)

Fig

u

re

1

6

.

Ser

ia

l Dat

a

Co

ding and Ext

ra

c

tion

Option

s within t

h

e TDM Stre

ams