Q-channel full-scale voltage adjust, Des enable, Des coarse adjust – Rainbow Electronics ADC08D1000 User Manual

Page 23: 0 functional description

1.0 Functional Description

(Continued)

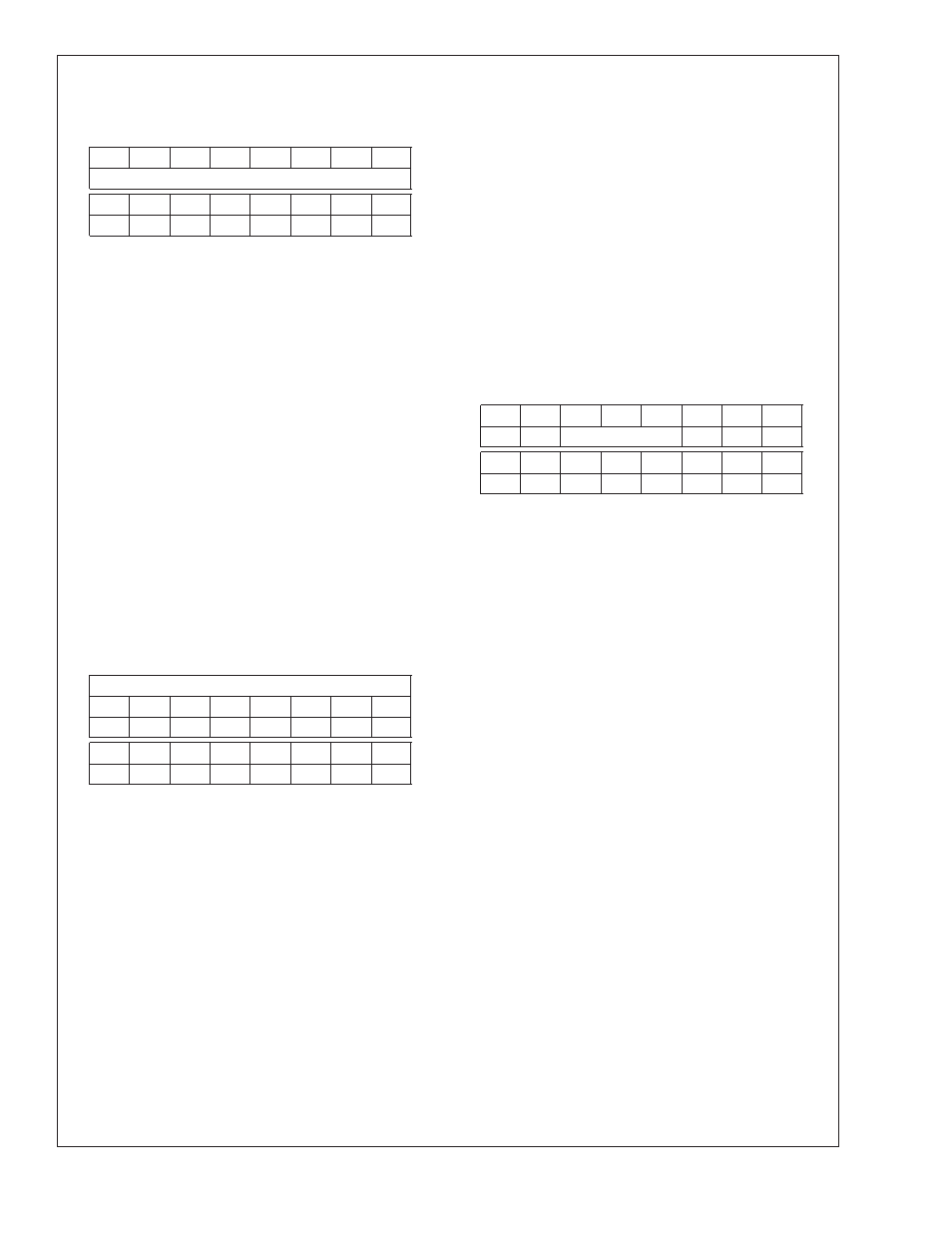

Q-Channel Full-Scale Voltage Adjust

Addr: Bh (1011b)

W only (0x807F)

D15

D14

D13

D12

D11

D10

D9

D8

(MSB)

Adjust Value

D7

D6

D5

D4

D3

D2

D1

D0

(LSB)

1

1

1

1

1

1

1

Bit 15:7

Full Scale Voltage Adjust Value. The input

full-scale voltage or gain of the I-Channel

ADC is adjusted linearly and monotonically

with a 9 bit data value. The adjustment

range is

±

20% of the nominal 700 mV

P-P

differential value.

0000 0000 0

560mV

P-P

1000 0000 0

700mV

P-P

1111 1111 1

840mV

P-P

For best performance, it is recommended

that the value in this field be limited to the

range of 0110 0000 0b to 1110 0000 0b.

i.e., limit the amount of adjustment to

±

15%.

The remaining

±

5% headroom allows for

the ADC’s own full scale variation. A gain

adjustment does not require ADC

re-calibration.

POR State: 1 0000 0000b (no adjustment)

Bits 6:0

Must be set to 1b

DES Enable

Addr: Dh (1101b)

W only (0x3FFF)

D15

D14

D13

D12

D11

D10

D9

D8

DEN

ACP

1

1

1

1

1

1

D7

D6

D5

D4

D3

D2

D1

D0

1

1

1

1

1

1

1

1

Bit 15

DES Enable. Setting this bit to 1b enables

the Dual Edge Sampling mode. In this mode

the ADCs in this device are used to sample

and convert the same analog input in a

time-interleaved manner, accomplishing a

sampling rate of twice the input clock rate.

When this bit is set to 1b, the device

operates in the normal dual channel mode.

POR State: 0b

Bit 14

Automatic Clock Phase Control. Setting this

bit to 1b enables the Automatic Clock Phase

Control. In this mode the DES Coarse and

Fine manual controls are disabled. A phase

detection circuit continually adjusts the I and

Q sampling edges to be 180 degrees out of

phase. When this bit is set to 1b, the

sample (input) clock delay between the I

and Q channels is set manually using the

DES Coarse and Fine Adjust registers. (See

Section 2.4.5 for important application

information)

POR State: 0b

Bits 13:0

Must be set to 1b

DES Coarse Adjust

Addr: Eh (1110b)

W only (0x07FF)

D15

D14

D13

D12

D11

D10

D9

D8

IS

ADS

CAM

1

1

1

D7

D6

D5

D4

D3

D2

D1

D0

1

1

1

1

1

1

1

1

Bit 15

Input Select. When this bit is set to 0b the "I"

input is operated upon by both ADCs. When

this bit is set to 1b the "Q" input is operated

on by both ADCs.

POR State: 0b

Bit 14

Adjust Direction Select. When this bit is set

to "0", the "I" channel sample clock is

delayed while the "Q" channel sample clock

remains fixed. When this bit is set to "1", the

"Q" channel sample clock is delayed while

the "I" channel sample clock remains fixed.

POR State: 0b

Bits 13:11 Coarse Adjust Magnitude. Each code value

in this field delays either the "I" channel or

the "Q" channel sample clock (as

determined by the ADS bit) by

approximately 20 picoseconds. A value of

000b in this field causes zero adjustment.

POR State: 000b

Bits 10:0 Must be set to 1b

ADC08D1000

www.national.com

23