The general purpose register file, The alu – arithmetic logic unit, The flash program memory – Rainbow Electronics ATtiny15L User Manual

Page 6: Attiny15l

6

ATtiny15L

1187E–AVR–06/02

A flexible interrupt module has its control registers in the I/O space with an additional

Global Interrupt Enable bit in the Status Register. All the different interrupts have a sep-

arate Interrupt Vector in the Interrupt Vector table at the beginning of the program

memory. The different interrupts have priority in accordance with their Interrupt Vector

position. The lower the Interrupt Vector address, the higher the priority.

The General Purpose

Register File

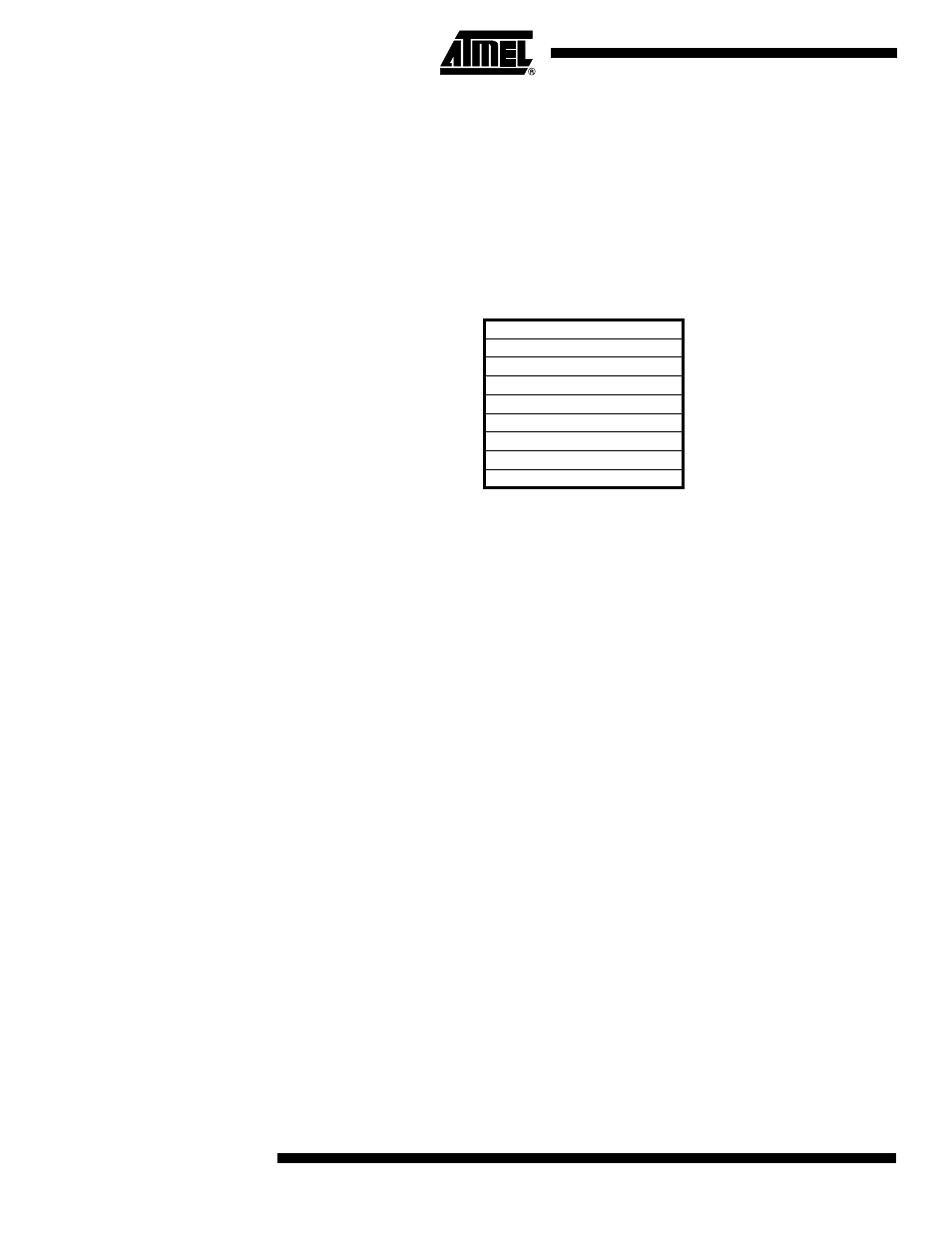

Figure 3 shows the structure of the 32 general purpose registers in the CPU.

Figure 3. AVR CPU General Purpose Working Registers

All the register operating instructions in the instruction set have direct- and single-cycle

access to all registers. The only exception is the five constant arithmetic and logic

instructions SBCI, SUBI, CPI, ANDI, and ORI between a constant and a register and the

LDI instruction for load-immediate constant data. These instructions apply to the second

half of the registers in the Register File – R16..R31. The general SBC, SUB, CP, AND,

OR, and all other operations between two registers or on a single-register apply to the

entire Register File.

Registers 30 and 31 form a 16-bit pointer (the Z-pointer) which is used for indirect Flash

memory and Register File access. When the Register File is accessed, the contents of

R31 is discarded by the CPU.

The ALU – Arithmetic

Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general

purpose working registers. Within a single clock cycle, ALU operations between regis-

ters in the Register File are executed. The ALU operations are divided into three main

categories – arithmetic, logic and bit-functions. Some microcontrollers in the AVR prod-

uct family feature a hardware multiplier in the arithmetic part of the ALU.

The Flash Program

Memory

The ATtiny15L contains 1K byte On-chip, In-System Programmable Flash memory for

program storage. Since all instructions are single 16-bit words, the Flash is organized as

512 x 16 words. The Flash memory has an endurance of at least 1,000 write/erase

cycles.

The ATtiny15L Program Counter is nine bits wide, thus addressing the 512 words Flash

Program memory.

See page 54 for a detailed description on Flash memory programming.

7

0

R0

R1

R2

General

…

Purpose

…

Working

R28

Registers

R29

R30 (Z-register Low Byte)

R3

R31 (Z-register High Byte)