Reset and interrupt handling, Attiny15l – Rainbow Electronics ATtiny15L User Manual

Page 12

12

ATtiny15L

1187E–AVR–06/02

• Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result after the different arithmetic and logic

operations. See the Instruction Set description for detailed information.

• Bit 1 – Z: Zero Flag

The Zero Flag Z indicates a zero result after the different arithmetic and logic opera-

tions. See the Instruction Set description for detailed information.

• Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the Instruction

Set description for detailed information.

Reset and Interrupt

Handling

The ATtiny15L provides eight interrupt sources. These interrupts and the separate

Reset Vector each have a separate Program Vector in the Program memory space. All

the interrupts are assigned individual enable bits that must be set (one) together with the

I-bit in the Status Register in order to enable the interrupt.

The lowest addresses in the Program memory space are automatically defined as the

Reset and Interrupt Vectors. The complete list of vectors is shown in Table 3. The list

also determines the priority levels of the different interrupts. The lower the address the

higher is the priority level. RESET has the highest priority, and next is INT0 (the External

Interrupt Request 0), etc.

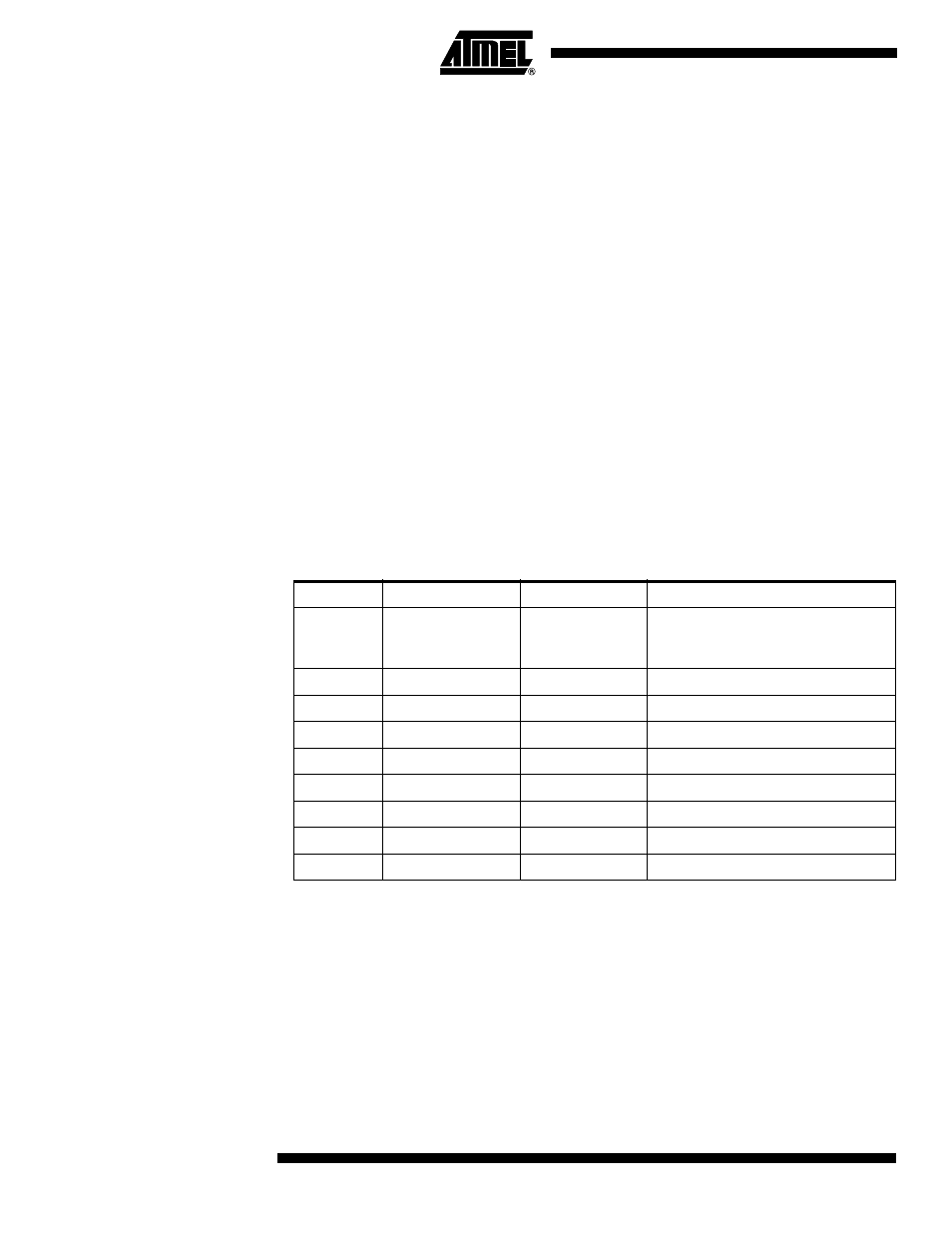

Table 3. Reset and Interrupt Vectors

Vector No.

Program Address

Source

Interrupt Definition

1

$000

RESET

External Reset, Power-on Reset,

Brown-out Reset, and Watchdog

Reset

2

$001

INT0

External Interrupt Request 0

3

$002

I/O Pins

Pin Change Interrupt

4

$003

TIMER1, COMPA

Timer/Counter1 Compare Match A

5

$004

TIMER1, OVF

Timer/Counter1 Overflow

6

$005

TIMER0, OVF

Timer/Counter0 Overflow

7

$006

EE_RDY

EEPROM Ready

8

$007

ANA_COMP

Analog Comparator

9

$008

ADC

ADC Conversion Complete