The timer/counter interrupt flag register – tifr, Attiny15l – Rainbow Electronics ATtiny15L User Manual

Page 21

21

ATtiny15L

1187E–AVR–06/02

vector $003) is executed if a compare match A in Timer/Counter1 occurs, i.e., when the

OCF1A bit is set (one) in the Timer/Counter Interrupt Flag Register (TIFR).

• Bit 5..3 – Res: Reserved Bits

These bits are reserved bits in the ATtiny15L and always read as zero.

• Bit 2 – TOIE1: Timer/Counter1 Overflow Interrupt Enable

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the

Timer/Counter1 Overflow interrupt is enabled. The corresponding interrupt (at vector

$004) is executed if an overflow in Timer/Counter1 occurs, i.e., when the TOV1 bit is set

(one) in the Timer/Counter Interrupt Flag Register (TIFR).

• Bit 1 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the

Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt (at vector

$005) is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set

(one) in the Timer/Counter Interrupt Flag Register (TIFR).

• Bit 0 – Res: Reserved Bit

This bit is a reserved bit in the ATtiny15L and always reads as zero.

The Timer/Counter Interrupt

Flag Register – TIFR

• Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the ATtiny15L and always reads as zero.

• Bit 6 – OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when compare match occurs between Timer/Counter1 and

the data value in OCR1A (Output Compare Register 1A). OCF1A is cleared by hard-

ware when executing the corresponding interrupt handling vector. Alternatively, OCF1A

is cleared by writing a logical “1” to the flag. When the I-bit in SREG, OCIE1A, and

OCF1A are set (one), the Timer/Counter1 compare match A interrupt is executed.

• Bits 5..3 – Res: Reserved bits

These bits are reserved bits in the ATtiny15L and always read as zero.

• Bit 2 – TOV1: Timer/Counter1 Overflow Flag

The bit TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared

by hardware when executing the corresponding interrupt handling vector. Alternatively,

TOV1 is cleared by writing a logical “1” to the flag. When the SREG I-bit, TOIE1

( T i m e r / C o u n te r1 O v e r f l o w In t e rr u p t En a b l e ) a n d T O V 1 a re s e t ( o n e ) , t h e

Timer/Counter1 Overflow Interrupt is executed.

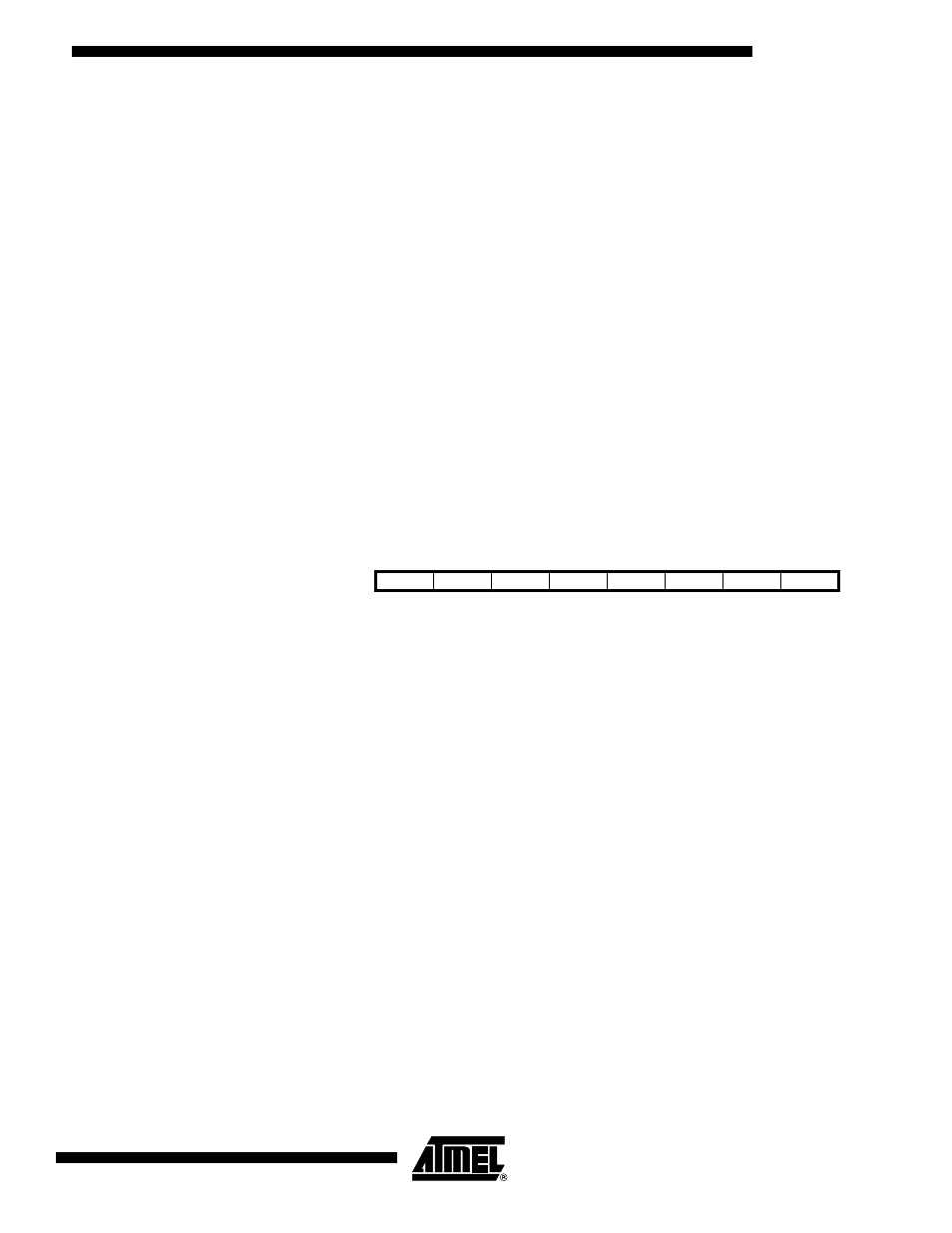

Bit

7

6

5

4

3

2

1

0

$38

–

OCF1A

–

–

–

TOV1

TOV0

–

TIFR

Read/Write

R

R/W

R

R

R

R/W

R/W

R

Initial Value

0

0

0

0

0

0

0

0