The timer counter 0 – tcnt0, The 8-bit timer/counter1, Attiny15l – Rainbow Electronics ATtiny15L User Manual

Page 28

28

ATtiny15L

1187E–AVR–06/02

The Timer Counter 0 – TCNT0

The Timer/Counter0 is implemented as an up-counter with read and write access. If the

Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues

counting in the timer clock cycle following the write operation.

The 8-bit Timer/Counter1

This module features a high-resolution and a high-accuracy usage with the lower pres-

caling opportunities. Timer/Counter1 can also be used as an accurate, high speed, 8-bit

Pulse Width Modulator (PWM) using clock speeds up to 25.6 MHz. In this mode,

Timer/Counter1 and the Output Compare Registers serve as a standalone PWM. Refer

to page 34 for a detailed description of this function. Similarly, the high-prescaling

opportunities make this unit useful for lower-speed functions or exact-timing functions

with infrequent actions.

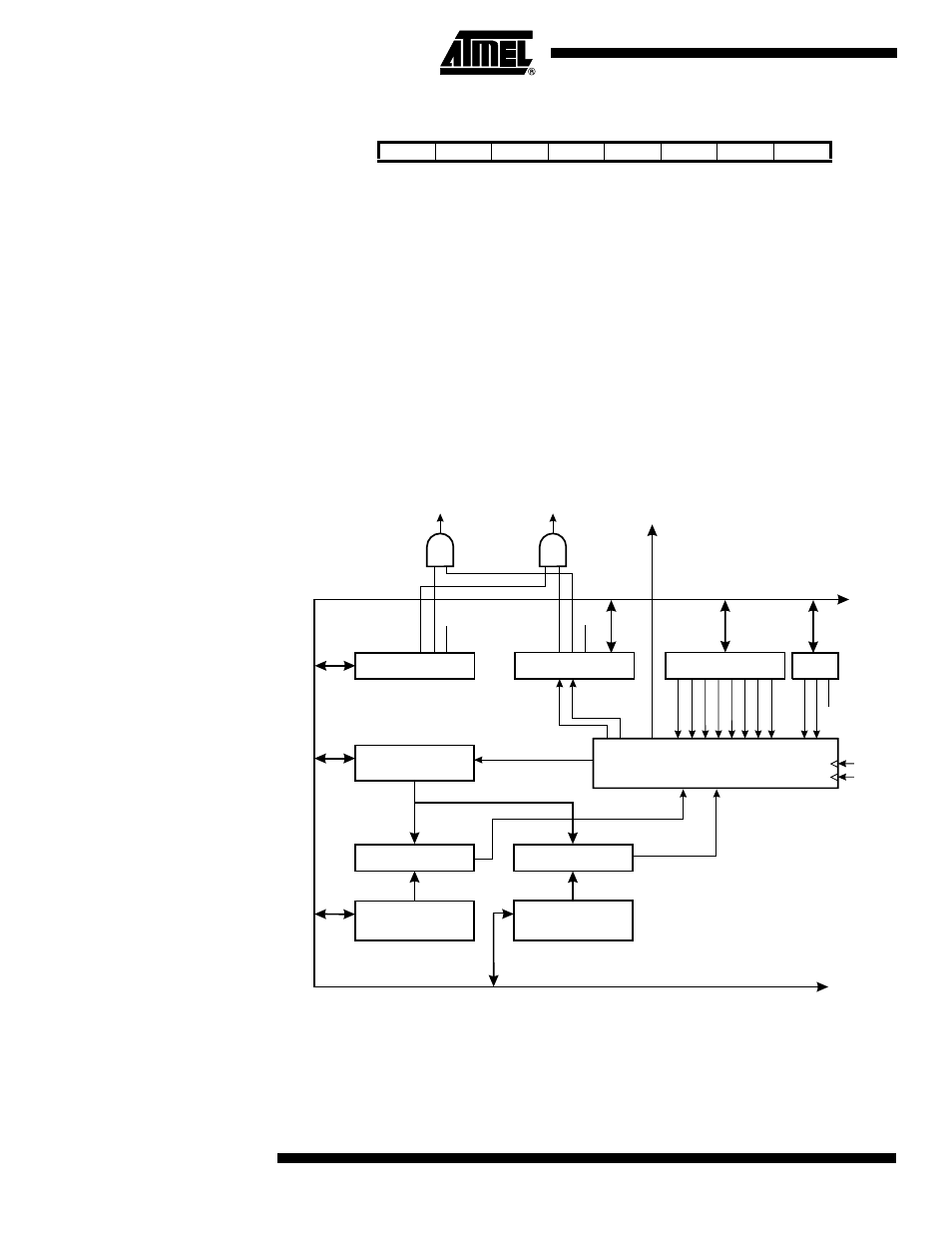

Figure 21 shows the block diagram for Timer/Counter1.

Figure 21. Timer/Counter1 Block Diagram

The two Status Flags (Overflow and Compare Match) are found in the Timer/Counter

Interrupt Flag Register (TIFR). Control signals are found in the Timer/Counter Control

Register (TCCR1). The interrupt enable/disable settings are found in the Timer/Counter

Interrupt Mask Register (TIMSK).

Bit

7

6

5

4

3

2

1

0

$32

MSB

LSB

TCNT0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

8-BIT DATA BUS

TIMER INT. FLAG

REGISTER (TIFR)

TIMER/COUNTER1

(TCNT1)

8-BIT COMPARATOR

T/C1 OUTPUT

T/C1 OUTPUT

COMPARE REGISTER A

COMPARE REGISTER B

TIMER INT. MASK

REGISTER (TIMSK)

T/C CLEAR

T/C1 CONTROL

LOGIC

TOV1

OCF1A

OCF1A

TOV1

TOIE0

TOIE1

OCIE1A

CK

PCK

T/C1 OVER-

FLOW IRQ

T/C1 A COMPARE

MATCH IRQ

T/C CONTROL

REGISTER 1 (TCCR1)

CS12

COM1A1

PWM1

CS11

COM1A0

CS10

CS13

(OCR1A)

8-BIT COMPARATOR

(OCR1B)

SFIOR

TOV0

FOC1

PSR1

CTC1

T/C1 OC1A PIN/

PORT PB1

(PWM OUTPUT)

PSR0