The timer/counter1 – tcnt1, Attiny15l – Rainbow Electronics ATtiny15L User Manual

Page 30

30

ATtiny15L

1187E–AVR–06/02

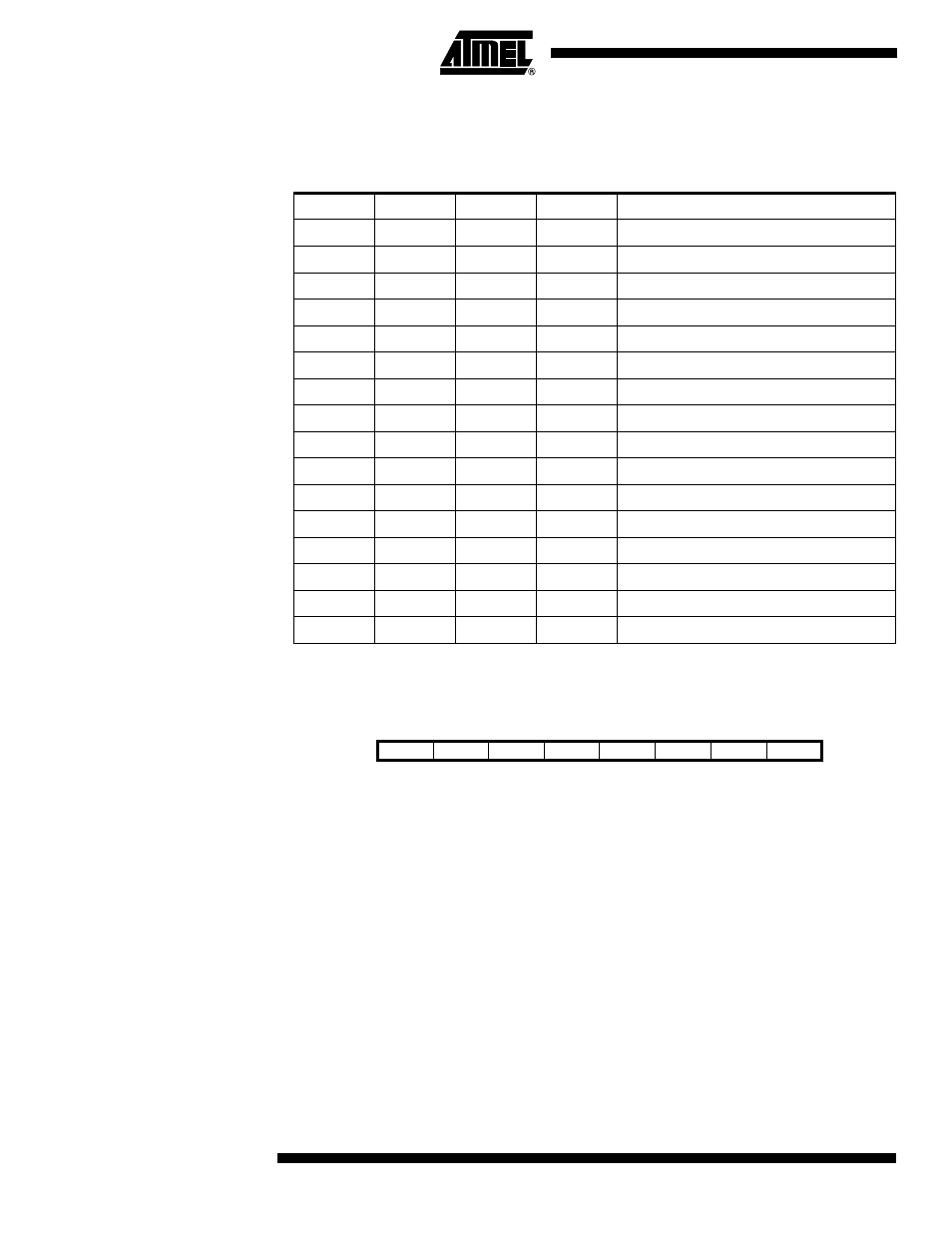

• Bits 3, 2, 1, 0 – CS13, CS12, CS11, CS10: Clock Select Bits 3, 2, 1, and 0

The Clock Select bits 3, 2, 1, and 0 define the prescaling source of Timer/Counter1.

The Stop condition provides a Timer Enable/Disable function. The prescaled CK modes

are scaled directly from the CK oscillator clock.

The Timer/Counter1 – TCNT1

This 8-bit register contains the value of Timer/Counter1.

Timer/Counter1 is implemented as an up-counter with read and write access. Due to

synchronization of the CPU and Timer/Counter1, data written into Timer/Counter1 is

delayed by one CPU clock cycle.

Table 11. Timer/Counter1 Prescale Select

CS13

CS12

CS11

CS10

Description

0

0

0

0

Timer/Counter1 is stopped.

0

0

0

1

CK*16 (=PCK)

0

0

1

0

CK*8 (=PCK/2)

0

0

1

1

CK*4 (=PCK/4)

0

1

0

0

CK*2 (=PCK/8)

0

1

0

1

CK

0

1

1

0

CK/2

0

1

1

1

CK/4

1

0

0

0

CK/8

1

0

0

1

CK/16

1

0

1

0

CK/32

1

0

1

1

CK/64

1

1

0

0

CK/128

1

1

0

1

CK/256

1

1

1

0

CK/512

1

1

1

1

CK/1024

Bit

7

6

5

4

3

2

1

0

$2F

MSB

LSB

TCNT1

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0