I/o port b, Alternative functions of port b, The port b data register – portb – Rainbow Electronics ATtiny15L User Manual

Page 51: The port b data direction register – ddrb, The port b input pins address – pinb, Attiny15l

51

ATtiny15L

1187E–AVR–06/02

I/O Port B

All AVR ports have true read-modify-write functionality when used as general digital I/O

ports. This means that the direction of one port pin can be changed without unintention-

ally changing the direction of any other pin with the SBI and CBI instructions. The same

applies for changing drive value (if configured as output) or enabling/disabling of pull-up

resistors (if configured as input).

Port B is a 6-bit bi-directional I/O port.

Three data memory address locations are allocated for Port B, one each for the Data

Register – PORTB, $18, Data Direction Register – DDRB, $17, and the Port B Input

Pins – PINB, $16. The Port B Input Pins address is read-only, while the Data Register

and the Data Direction Register are read/write.

Ports PB5..0 have special functions as described in the section “Pin Descriptions” on

page 4. If PB5 is not configured as External Reset, it is input with no pull-up or as an

open-drain output. All I/O pins have individually selectable pull-ups, which can be over-

ridden with pull-up disable.

The Port B output buffers on PB0 to PB4 can sink 20 mA and thus drive LED displays

directly. PB5 can sink 12 mA. When pins PB0 to PB4 are used as inputs and are exter-

nally pulled low, they will source current (I

IL

) if the internal pull-ups are activated.

Alternative Functions of

Port B

In ATtiny15L four Port B pins – PB2, PB3, PB4, and PB5 – have alternative functions as

inputs for the ADC. If some Port B pins are configured as outputs, it is essential that

these do not switch when a conversion is in progress. This might corrupt the result of the

conversion. During Power-down mode and ADC Noise Reduction mode, the Schmitt

triggers of the digital inputs are disconnected on these pins. This allows an analog input

voltage close to V

CC

/2 to be present during Power-down without causing excessive

power consumption. The Port B pins with alternate functions are shown in Table 1 on

page 4.

When the pins PB4..0 are used for the alternate function, the DDRB and PORTB Regis-

ters have to be set according to the alternate function description. When PB5 is used as

External Reset pin, the values in the corresponding DDRB and PORTB bit are ignored.

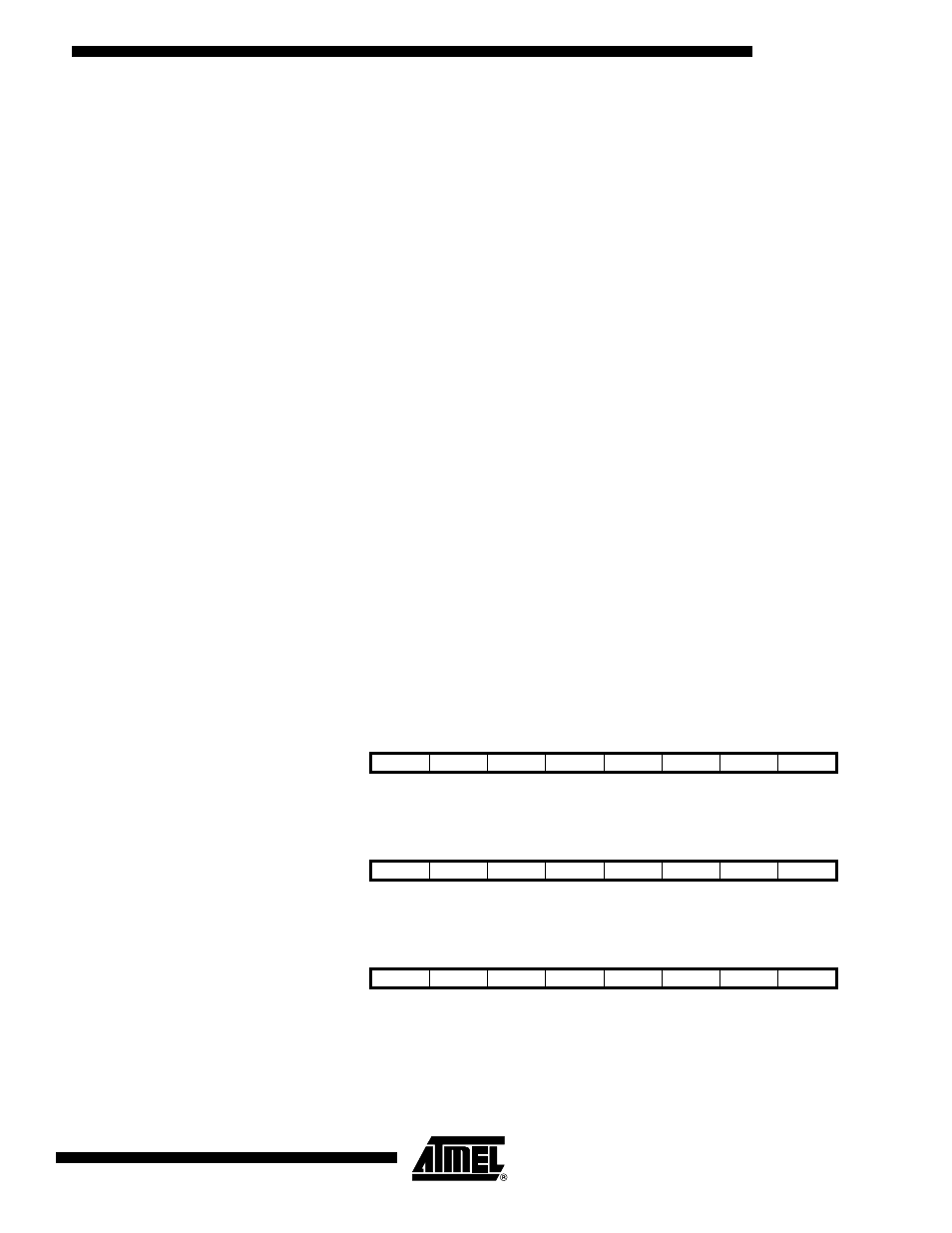

The Port B Data Register –

PORTB

The Port B Data Direction

Register – DDRB

The Port B Input Pins Address

– PINB

The Port B Input Pins address (PINB) is not a register, and this address enables access

to the physical value on each Port B pin. When reading PORTB, the PORTB Data Latch

is read, and when reading PINB, the logical values present on the pins are read.

Bit

7

6

5

4

3

2

1

0

$18

–

–

–

PORTB4

PORTB3

PORTB2

PORTB1

PORTB0

PORTB

Read/Write

R

R

R

R/W

R/WS

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

$17

–

–

DDB5

DDB4

DDB3

DDB2

DDB1

DDB0

DDRB

Read/Write

R

R

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

$16

–

–

PINB5

PINB4

PINB3

PINB2

PINB1

PINB0

PINB

Read/Write

R

R

R

R

R

R

R

R

Initial Value

0

0

N/A

N/A

N/A

N/A

N/A

N/A