The special function io register – sfior, The 8-bit timer/counter0, Attiny15l – Rainbow Electronics ATtiny15L User Manual

Page 26

26

ATtiny15L

1187E–AVR–06/02

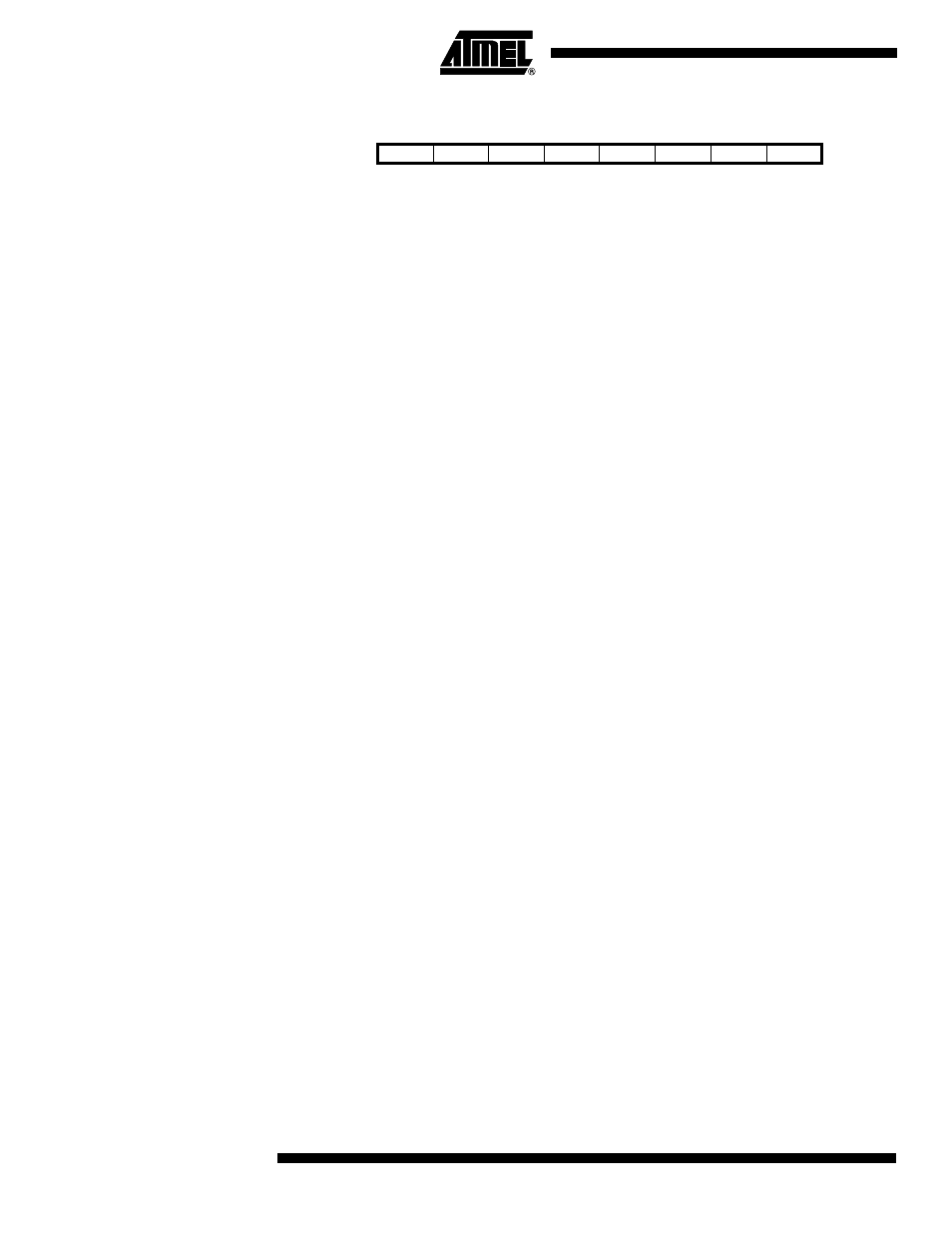

The Special Function IO

Register – SFIOR

• Bit 7..3 – Res: Reserved Bits

These bits are reserved bits in the ATtiny15L and always read as zero.

• Bit 2 – FOC1A: Force Output Compare 1A

Writing a logical “1” to this bit forces a change in the Compare Match Output pin PB1

(OC1A) according to the values already set in COM1A1 and COM1A0. The Force Out-

put Compare bit can be used to change the output pin without waiting for a compare

match in timer. The automatic action programmed in COM1A1 and COM1A0 happens

a s if a Co mp are M a tch had occurre d, bu t n o in te rrupt i s gen erated and th e

Timer/Counter1 will not be cleared even if CTC1 is set. The FOC1A bit will always be

read as zero. The setting of the FOC1A bit has no effect in PWM mode.

• Bit 1 – PSR1: Prescaler Reset Timer/Counter1

When this bit is set (one) the Timer/Counter1 prescaler will be reset. The bit will be

cleared by hardware after the operation is performed. Writing a “0” to this bit will have no

effect. This bit will always be read as zero.

• Bit 0 – PSR0: Prescaler Reset Timer/Counter0

When this bit is set (one) the Timer/Counter0 prescaler will be reset. The bit will be

cleared by hardware after the operation is performed. Writing a “0” to this bit will have no

effect. This bit will always be read as zero.

The 8-bit Timer/Counter0

Figure 20 shows the block diagram for Timer/Counter0.

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK or an external

p in . In a dd i tio n, i t can b e sto pp ed as de scri be d i n the spe ci fica tio n fo r th e

Timer/Counter0 Control Register (TCCR0). The Overflow Status Flag is found in the

Timer/Counter Interrupt Flag Register (TIFR). Control signals are found in the

Timer/Counter0 Control Register (TCCR0). The interrupt enable/disable settings for

Timer/Counter0 are found in the Timer/Counter Interrupt Mask Register (TIMSK).

When Timer/Counter0 is externally clocked, the external signal is synchronized with the

oscillator frequency of the CPU. To ensure proper sampling of the external clock, the

minimum time between two external clock transitions must be at least one internal CPU

clock period. The external clock signal is sampled on the rising edge of the internal CPU

clock.

The 8-bit Timer/Counter0 features both a high-resolution and a high-accuracy usage

with the lower prescaling opportunities. Similarly, the high-prescaling opportunities

make the Timer/Counter0 useful for lower-speed functions or exact-timing functions with

infrequent actions.

Bit

7

6

5

4

3

2

1

0

$2C

–

–

–

–

–

FOC1A

PSR1

PSR0

SFIOR

Read/Write

R

R

R

R

R

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0