Ata6823 [preliminary, 4 5v/3.3v vcc regulator, 5 reset and watchdog management – Rainbow Electronics ATA6823 User Manual

Page 9

9

4856E–AUTO–07/07

ATA6823 [Preliminary]

5.4

5V/3.3V VCC Regulator

The 5V/3.3V regulator is fully integrated on-chip. It requires only a 2.2 µF ceramic capacitor for

stability and has 100 mA current capability. Using the VMODE pin, the output voltage can be

selected to either 5V or 3.3V. Switching of the output voltage during operation is not intended to

be supported. The VMODE pin must be hard-wired to either VINT for 5V or to GND for 3.3V. The

logic HIGH level of the microcontroller interface will be adapted to the VCC regulator voltage.

The output voltage accuracy is in general < ±3%; in the 5V mode with V

VBAT

< 8V it is limited to

< 5%.

To prevent destruction of the IC, the current delivered by the regulator is limited to maximum

160 mA to 320 mA. The delivered voltage will break down and a reset may occur.

Please note that this regulator is the main heat source on the chip. The maximum output current

at maximum battery voltage and high ambient temperature can only guaranteed if the IC is

mounted on an efficient heat sink.

A power-good comparator checks the output voltage of the VCC regulator and keeps the exter-

nal microcontroller in reset as long as the voltage is too low.

5.5

Reset and Watchdog Management

The timing basis of the watchdog is provided by the trimmed internal oscillator. Its period T

OSC

is

adjustable via the external resistor R

WD

.

The watchdog expects a triggering signal (a rising edge) from the microcontroller at the WD

input within a period time window of T

WD

. In order to save current consumption, the watchdog is

switched off during Sleep mode.

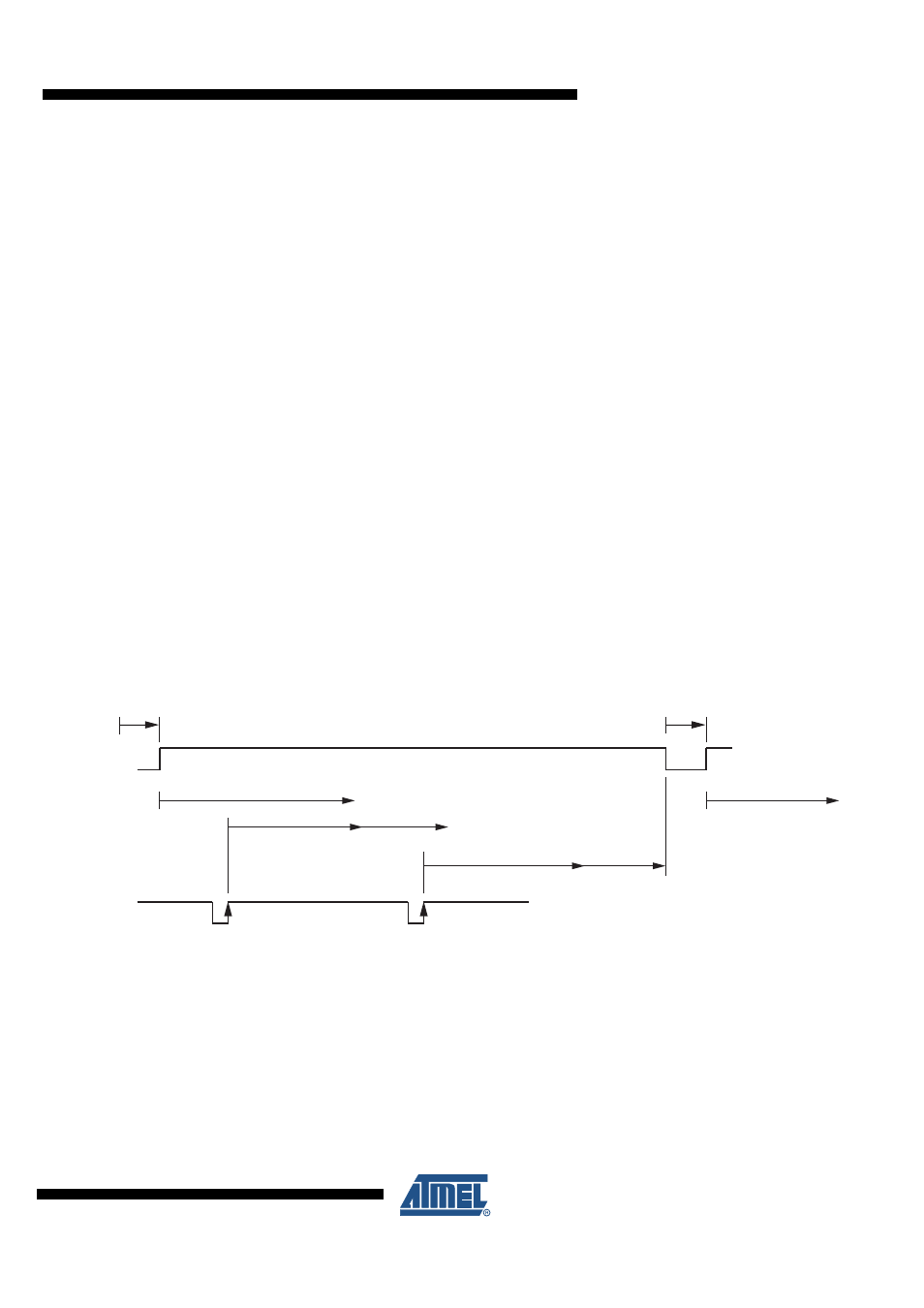

Figure 5-2.

Timing Diagram of the Watchdog Function

5.5.1

Timing Sequence

For example, with an external resistor R

WD

= 33 k

Ω

±1% we get the following typical parameters

of the watchdog.

T

OSC

= 12.32 µs, t

1

= 12.1 ms, t

2

= 9.61 ms, T

WD

= 16.88 ms ±10%

The times t

res

= 68 ms and t

d

= 68 ms are fixed values with a tolerance of 10%.

t

2

t

1

t

2

t

1

t

d

t

d

t

resshort

t

res

WD

/RESET