Bit synchronous mode – Rainbow Electronics T48C862-R4 User Manual

Page 69

69

T48C862-R4

4551B–4BMCU–02/03

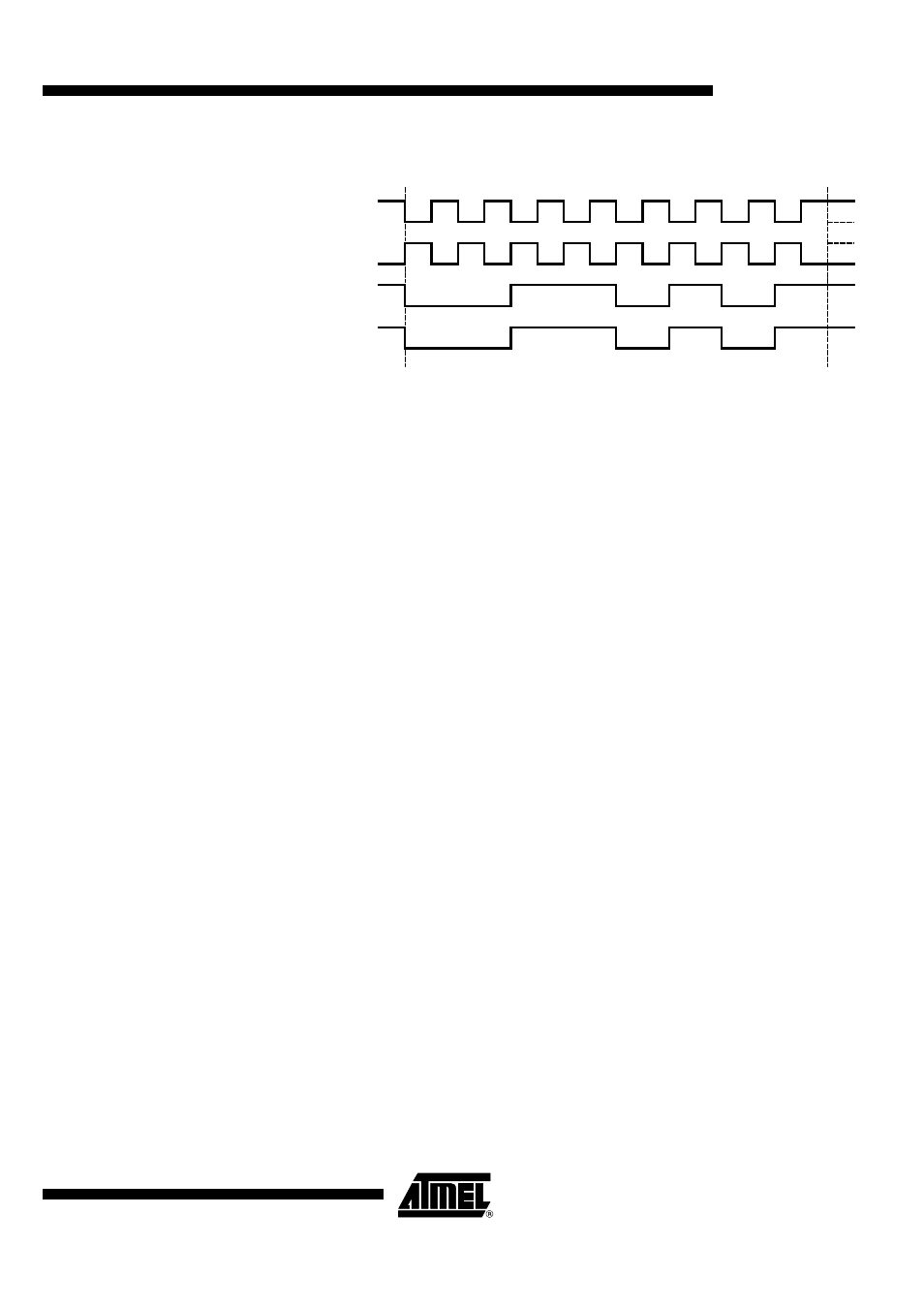

8-bit Synchronous Mode

Figure 65.

8-bit Synchronous Mode

In the 8-bit synchronous mode, the SSI can operate as either a 2- or 3-wire interface

(see SSI peripheral configuration). The serial data (SD) is received or transmitted in

NRZ format, synchronized to either the rising or falling edge of the shift clock (SC). The

choice of clock edge is defined by the Serial Mode Control bits (SM0,SM1). It should be

noted that

the transmission edge refers to the SC clock edge with which the SD

changes. To avoid clock skew problems, the incoming serial input data is shifted in with

the opposite edge.

When used together with one of the timer modulator or demodulator stages, the SSI

must be set in the 8-bit synchronous mode 1.

In RX mode, as soon as the SSI is activated (SIR = 0), 8 shift clocks are generated and

the incoming serial data is shifted into the shift register. This first telegram is automati-

cally transferred into the receive buffer and the SRDY set to 0 indicating that the receive

buffer contains valid data. At the same time an interrupt (if enabled) is generated. The

SSI then continues shifting in the following 8-bit telegram. If, during this time the first

telegram has been read by the controller, the second telegram will also be transferred in

the same way into the receive buffer and the SSI will continue clocking in the next tele-

gram. Should, however, the first telegram not have been read (SRDY = 1), then the SSI

will stop, temporarily holding the second telegram in the shift register until a certain point

of time when the controller is able to service the receive buffer. In this way no data is lost

or overwritten.

Deactivating the SSI (SIR = 1) in mid-telegram will immediately stop the shift clock and

latch the present contents of the shift register into the receive buffer. This can be used

for clocking in a data telegram of less than 8 bits in length. Care should be taken to read

out the final complete 8-bit data telegram of a multiple word message before deactivat-

ing the SSI (SIR = 1) and terminating the reception. After termination, the shift register

contents will overwrite the receive buffer.

SC

SC

DATA

SD/TO2

1

1

0

1

0

1

0

0

Bit 7

Bit 0

1

1

0

1

0

1

0

0

Bit 7

Bit 0

Data: 00110101

(Rising edge)

(Falling edge)