I/o bus, Instruction set, Interrupt structure – Rainbow Electronics T48C862-R4 User Manual

Page 18

18

T48C862-R4

4551B–4BMCU–02/03

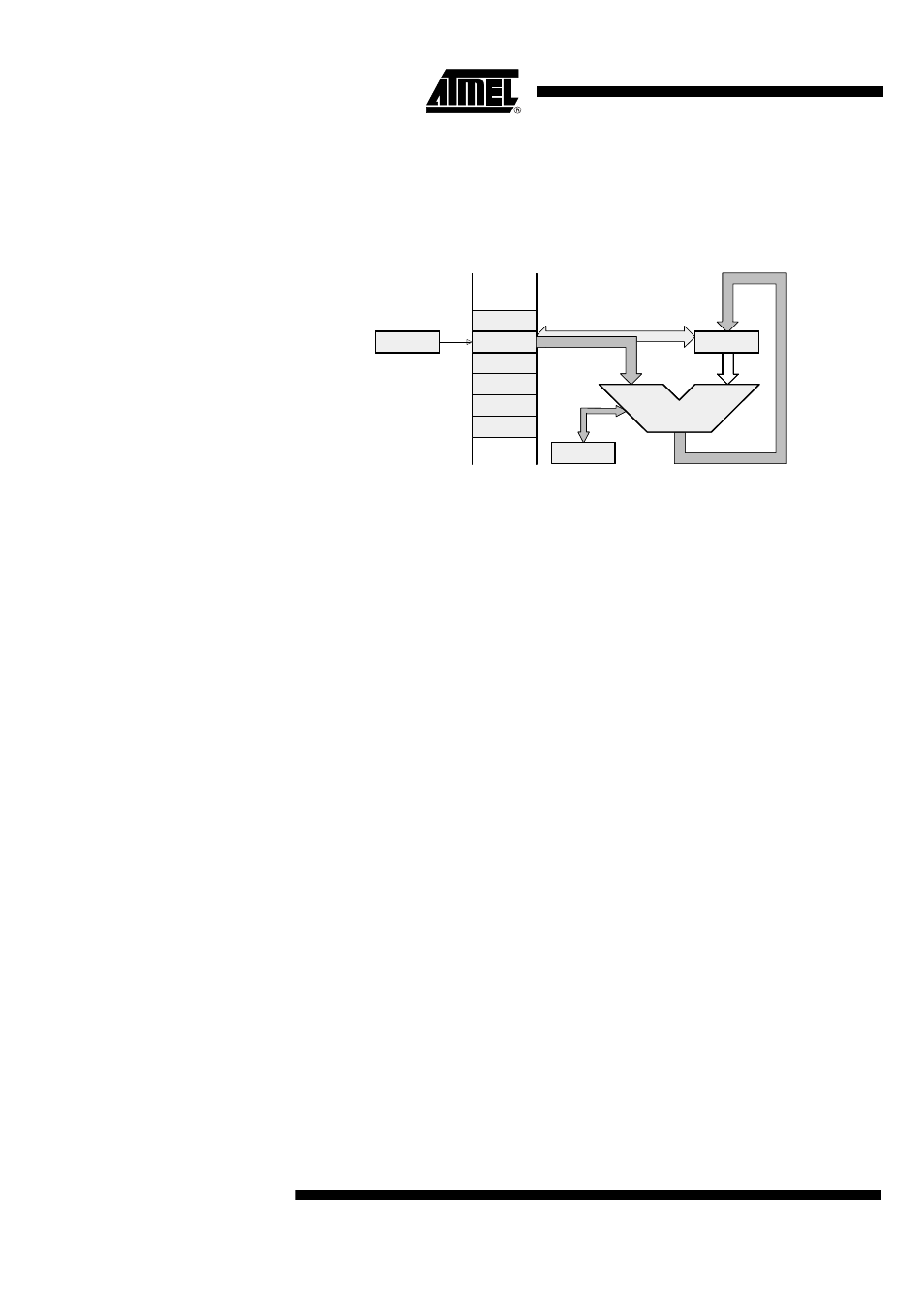

ALU

The 4-bit ALU performs all the arithmetic, logical, shift and rotate operations with the top

two elements of the expression stack (TOS and TOS-1) and returns the result to the

TOS. The ALU operations affects the carry/borrow and branch flag in the condition code

register (CCR).

Figure 13.

ALU Zero-address Operations

I/O Bus

The I/O ports and the registers of the peripheral modules are I/O mapped. All communi-

cation between the core and the on-chip peripherals take place via the I/O bus and the

associated I/O control. With the microcontroller IN and OUT instructions, the I/O bus

allows a direct read or write access to one of the 16 primary I/O addresses. More about

the I/O access to the on-chip peripherals is described in the section“”Peripheral Mod-

ules”. The I/O bus is internal and is not accessible by the customer on the final

microcontroller device, but it is used as the interface for the microcontroller emulation

(see also the section“”Emulation”).

Instruction Set

The microcontroller instruction set is optimized for the high level programming language

qFORTH. Many microcontroller instructions are qFORTH words. This enables the com-

piler to generate a fast and compact program code. The CPU has an instruction pipeline

allowing the controller to prefetch an instruction from EEPROM at the same time as the

present instruction is being executed. The microcontroller is a zero-address machine,

the instructions contain only the operation to be performed and no source or destination

address fields. The operations are implicitly performed on the data placed on the stack.

There are one- and two-byte instructions which are executed within 1 to 4 machine

c y c le s . A m i c r o co n t r o ll e r m a c h i n e c y c le is m a d e u p o f t w o s y s t e m c l o c k

cycles (SYSCL). Most of the instructions are only one byte long and are executed in a

single machine cycle. For more information refer to the “MARC4 Programmer’s Guide”.

Interrupt Structure

The microcontroller can handle interrupts with eight different priority levels. They can be

generated from the internal and external interrupt sources or by a software interrupt

from the CPU itself. Each interrupt level has a hard-wired priority and an associated vec-

tor for the service routine in the EEPROM (see Table 1). The programmer can postpone

the processing of interrupts by resetting the interrupt enable flag (I) in the CCR. An inter-

rupt occurrence will still be registered, but the interrupt routine only started after the

I-flag is set. All interrupts can be masked, and the priority individually software config-

ured by programming the appropriate control register of the interrupting module (see

section “Peripheral Modules”).

TOS-1

CCR

RAM

TOS-2

SP

TOS-3

TOS

ALU

TOS-4