Table 4-2. bit definitions for the standard event, 4 alarm registers, Alarm registers – American Magnetics 187 Self-Compensating Liquid Level Controller User Manual

Page 46: Remote interface reference

35

Remote Interface Reference

SCPI Status System

4.2.4

Alarm Registers

The Alarm register group reports the present condition of all alarms in the

Alarm Condition register, and latches the ON state of all alarms in the

Alarm Event register.

Any or all of the bits in the Alarm Event register can be reported to the

Status Byte register by enabling the corresponding bit(s) in the Alarm

Event enable register (see Figure 4-1). To set the Alarm Event enable

register, write a binary-weighted decimal value using the

STATus:ALARm:ENABle

<

value

>

command.

The bit definitions for the Alarm Condition and Event registers are

identical and are provided in Table 4-3. The Alarm Condition register is

continually updated for each level measurement is available. The Alarm

Event register latches the occurrences of each alarm and the respective

bit(s) remain set until cleared.

The Alarm Event register is cleared when:

W

The

*CLS

(clear status) command is executed.

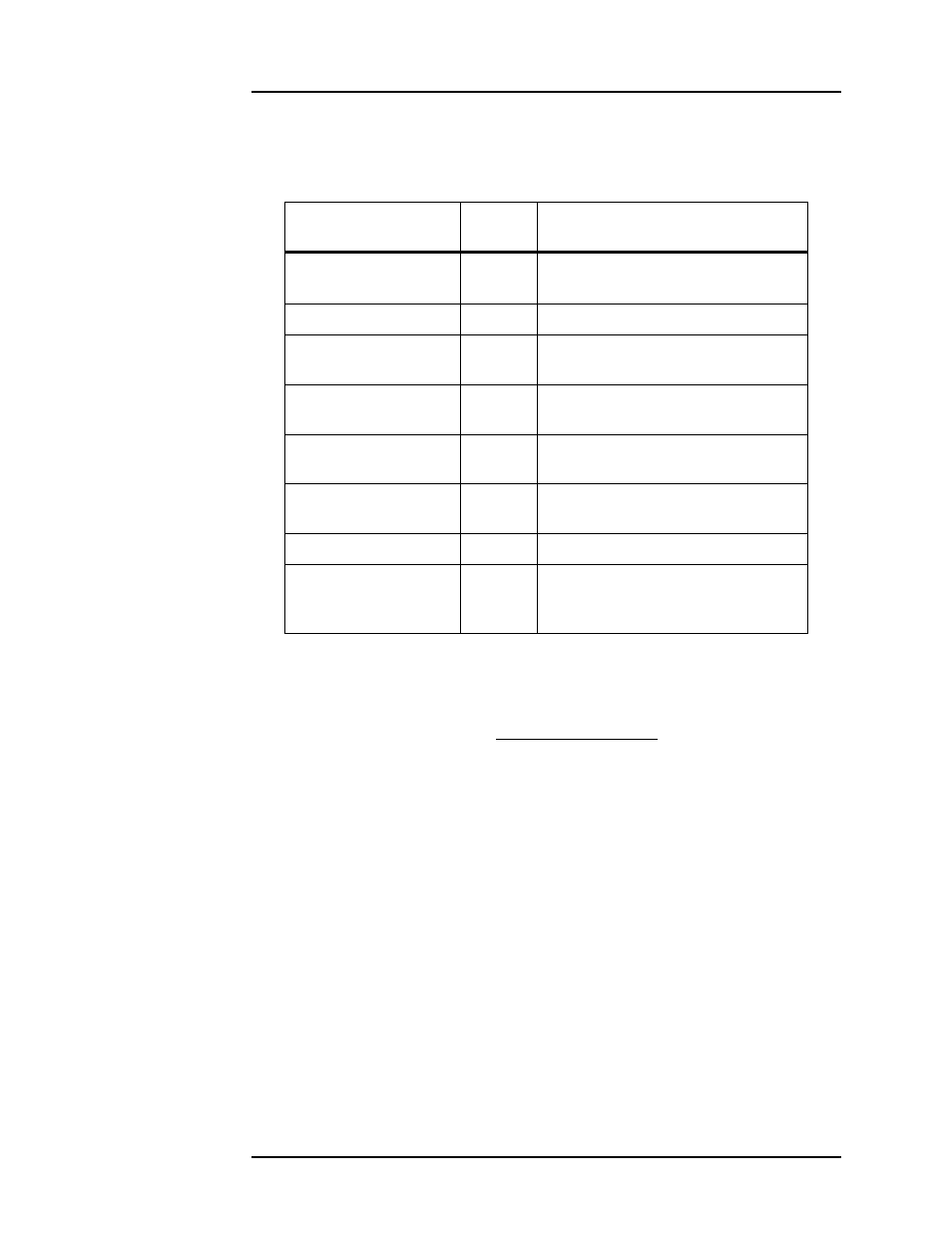

Table 4-2. Bit definitions for the Standard Event register.

Bit Number

Decimal

Value

Definition

0 Operation Complete

1

All commands prior to and including

*OPC

have been executed.

1

Not Used

2

Always “0”.

2 Query Error

4

A query error occurred. See the

error messages in the -200 range.

3 Device Error

8

A device error occurred. See the

error messages in the -400 range.

4 Execution Error

16

An execution error occurred. See the

error messages in the -300 range.

5 Command Error

32

A command error occurred. See the

error messages in the -100 range.

6

Not Used

64

Always “0”.

7 Power On

128

Power has been cycled since the

last time the Standard Event register

was read or cleared.