Descriptions, Figure 24, Table 13 – Texas Instruments TMS320DM644x User Manual

Page 29

www.ti.com

Registers

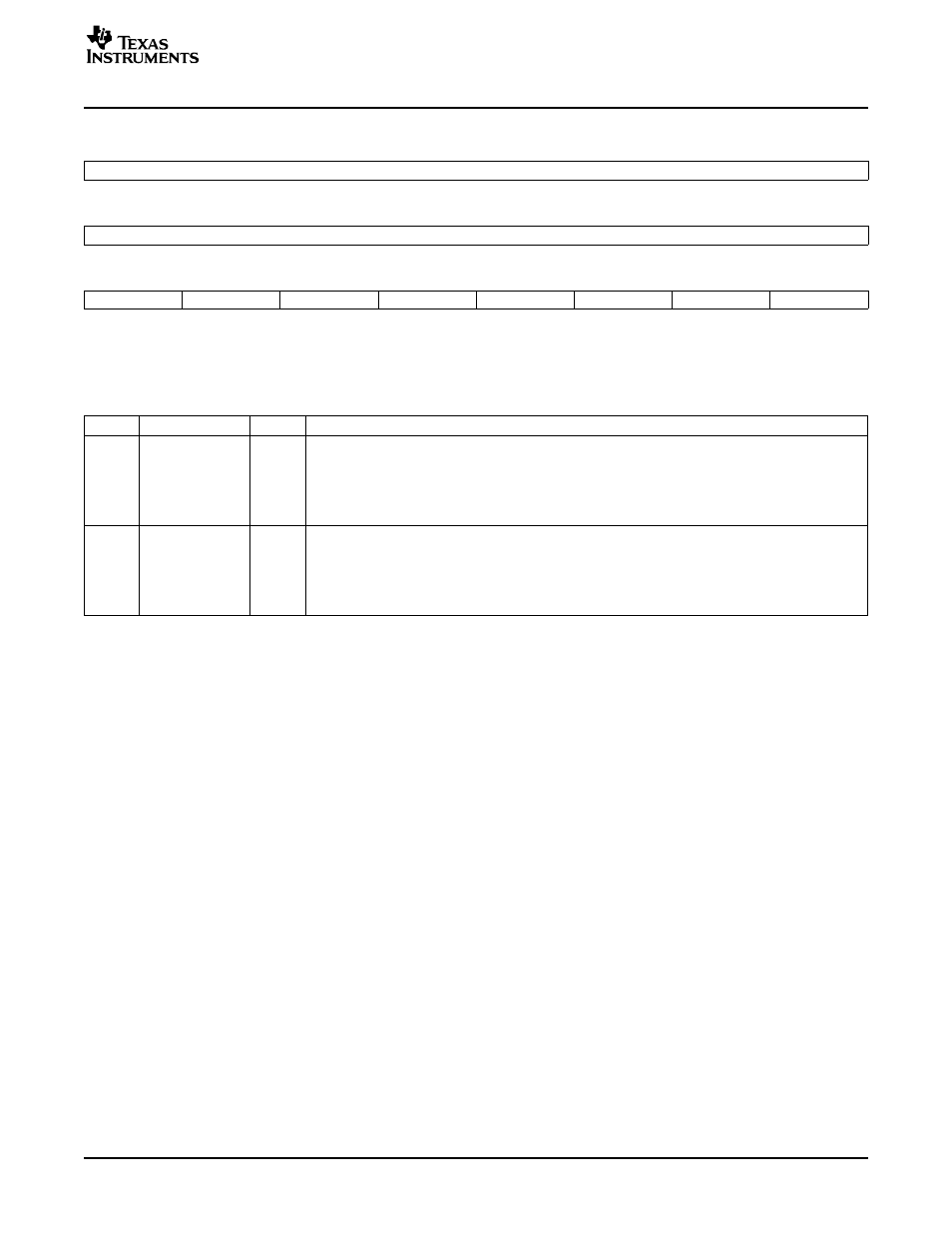

Figure 24. GPIO Bank 4 Clear Rising Edge Interrupt Register (CLR_RIS_TRIG4)

31

16

Reserved

R-0

15

8

Reserved

R-0

7

6

5

4

3

2

1

0

Reserved

CLRRIS70

CLRRIS69

CLRRIS68

CLRRIS67

CLRRIS66

CLRRIS65

CLRRIS64

R-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 13. GPIO Clear Rising Edge Interrupt Register (CLR_RIS_TRIGn) Field Descriptions

Bit

Field

Value

Description

31-16

CLRRISn

Disable rising edge interrupt detection on GPIO pin n. Reading the CLRRISn bit returns the

complement state of pin n on GPIO bank 2I + 1. This bit field configures the GPIO pins on GPIO

banks 1 and 3.

0

No effect.

1

No interrupt is caused by a low-to-high transition on GPIO pin n.

15-0

CLRRISn

Disable rising edge interrupt detection on GPIO pin n. Reading the CLRRISn bit returns the

complement state of pin n on GPIO bank 2I. This bit field configures the GPIO pins on GPIO banks

0, 2, and 4.

0

No effect.

1

No interrupt is caused by a low-to-high transition on GPIO pin n.

SPRUE25 – December 2005

General-Purpose Input/Output (GPIO)

29