3 gpio direction registers (dirn), Dir4), Descriptions – Texas Instruments TMS320DM644x User Manual

Page 19: Section 3.3

www.ti.com

3.3

GPIO Direction Registers (DIRn)

Registers

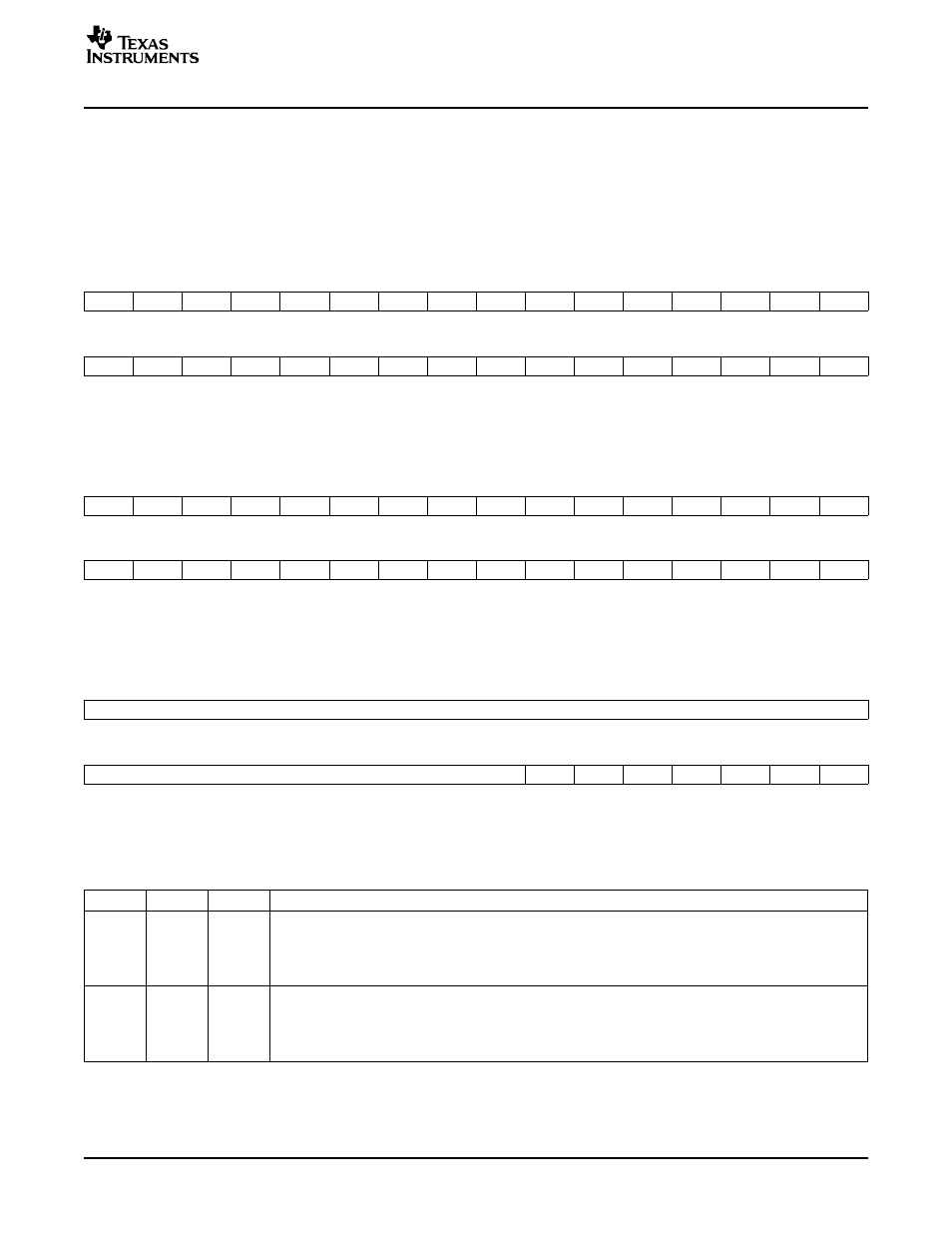

The GPIO direction register (DIRn) determines if GPIO pin n in GPIO bank I is an input or an output. Each

of the GPIO banks may have up to 16 GPIO pins. By default, all the GPIO pins are configured as inputs

(bit value = 1). The GPIO direction register (DIR01) is shown in

, DIR23 is shown in

,

DIR4 is shown in

, and described in

. See

to determine the DIRn bit associated

with each GPIO bank and pin number.

Figure 4. GPIO Banks 0 and 1 Direction Register (DIR01)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

DIR31

DIR30

DIR29

DIR28

DIR27

DIR26

DIR25

DIR24

DIR23

DIR22

DIR21

DIR20

DIR19

DIR18

DIR17

DIR16

R/W-1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DIR15

DIR14

DIR13

DIR12

DIR11

DIR10

DIR9

DIR8

DIR7

DIR6

DIR5

DIR4

DIR3

DIR2

DIR1

DIR0

R/W-1

LEGEND: R/W = Read/Write; -n = value after reset

Figure 5. GPIO Banks 2 and 3 Direction Register (DIR23)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

DIR63

DIR62

DIR61

DIR60

DIR59

DIR58

DIR57

DIR56

DIR55

DIR54

DIR53

DIR52

DIR51

DIR50

DIR49

DIR48

R/W-1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

DIR47

DIR46

DIR45

DIR44

DIR43

DIR42

DIR41

DIR40

DIR39

DIR38

DIR37

DIR36

DIR35

DIR34

DIR33

DIR32

R/W-1

LEGEND: R/W = Read/Write; -n = value after reset

Figure 6. GPIO Bank 4 Direction Register (DIR4)

31

16

Reserved

R-0

15

7

6

5

4

3

2

1

0

Reserved

DIR70

DIR69

DIR68

DIR67

DIR66

DIR65

DIR64

R-0

R/W-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7. GPIO Direction Register (DIRn) Field Descriptions

Bit

Field

Value

Description

31-16

DIRn

Direction of GPIO pin n. The DIRn bit is used to control the direction (output = 0, input = 1) of pin n on

GPIO bank 2I + 1. This bit field configures the GPIO pins on GPIO banks 1 and 3.

0

GPIO pin n is an output.

1

GPIO pin n is an input.

15-0

DIRn

Direction of GPIO pin n. The DIRn bit is used to control the direction (output = 0, input = 1) of pin n on

GPIO bank 2I. This bit field configures the GPIO pins on GPIO banks 0, 2, and 4.

0

GPIO pin n is an output.

1

GPIO pin n is an input.

SPRUE25 – December 2005

General-Purpose Input/Output (GPIO)

19