2 gpio interrupt per-bank enable register (binten), Binten), Descriptions – Texas Instruments TMS320DM644x User Manual

Page 18: Section 3.2

www.ti.com

3.2

GPIO Interrupt Per-Bank Enable Register (BINTEN)

Registers

The GPIO interrupt per-bank enable register (BINTEN) is shown in

and described in

. For

information on which GPIO signals are associated with each bank, see

.

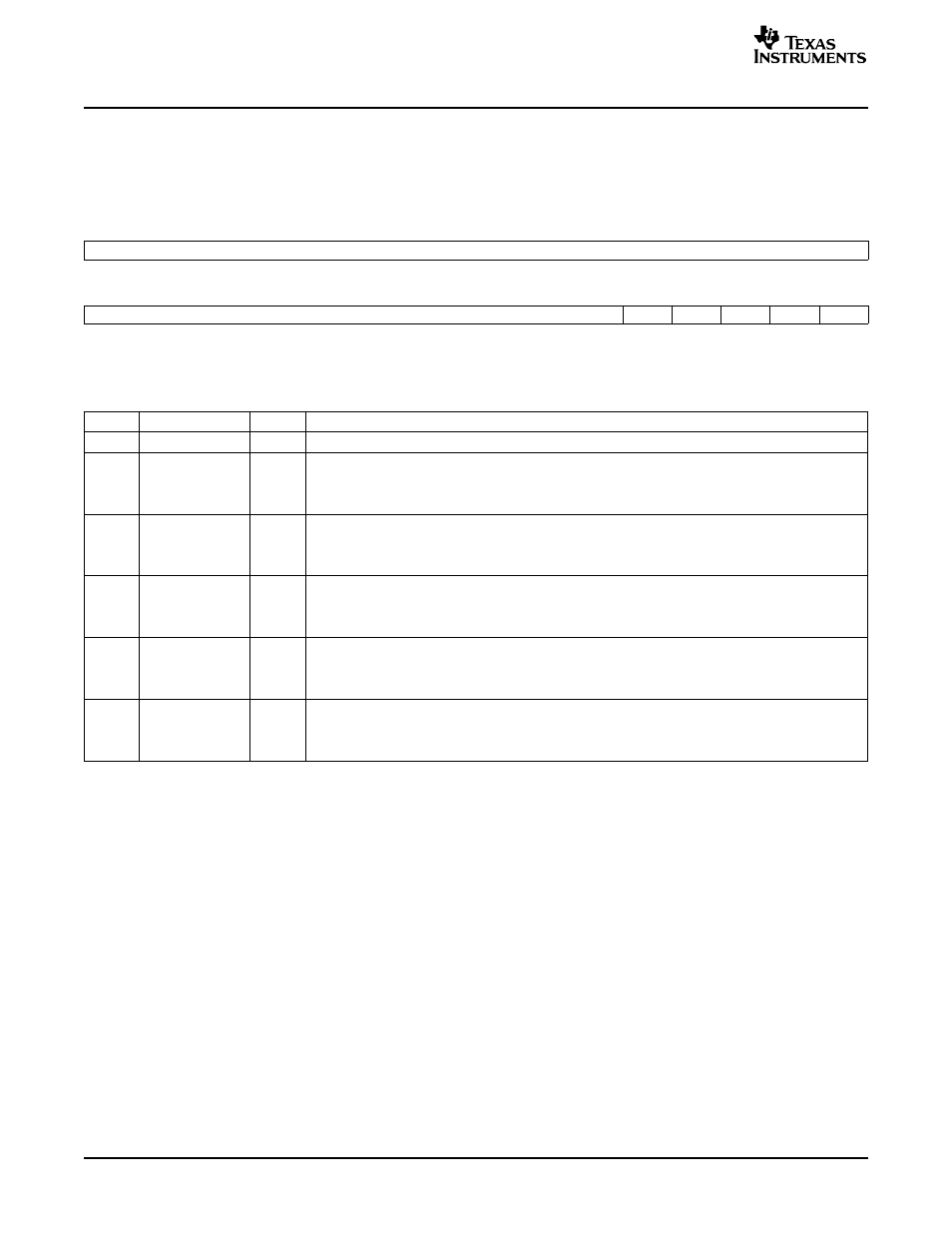

Figure 3. GPIO Interrupt Per-Bank Enable Register (BINTEN)

31

16

Reserved

R-0

15

5

4

3

2

1

0

Reserved

EN4

EN3

EN2

EN1

EN0

R-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 6. GPIO Interrupt Per-Bank Enable Register (BINTEN) Field Descriptions

Bit

Field

Value

Description

31-5

Reserved

0

Reserved

4

EN4

Bank 4 interrupt enable is used to disable or enable the bank 4 interrupts.

0

Bank 4 interrupts are disabled.

1

Bank 4 interrupts are enabled.

3

EN3

Bank 3 interrupt enable is used to disable or enable the bank 3 interrupts.

0

Bank 3 interrupts are disabled.

1

Bank 3 interrupts are enabled.

2

EN2

Bank 2 interrupt enable is used to disable or enable the bank 2 interrupts.

0

Bank 2 interrupts are disabled.

1

Bank 2 interrupts are enabled.

1

EN1

Bank 1 interrupt enable is used to disable or enable the bank 1 interrupts.

0

Bank 1 interrupts are disabled.

1

Bank 1 interrupts are enabled.

0

EN0

Bank 0 interrupt enable is used to disable or enable the bank 0 interrupts.

0

Bank 0 interrupts are disabled.

1

Bank 0 interrupts are enabled.

General-Purpose Input/Output (GPIO)

18

SPRUE25 – December 2005