C bus controller – Lucent Technologies MN10285K User Manual

Page 296

I

2

C Bus Controller

Description

MN102H75K/F75K/85K/F85K LSI User Manual

Panasonic Semiconductor Development Company

295

Panasonic

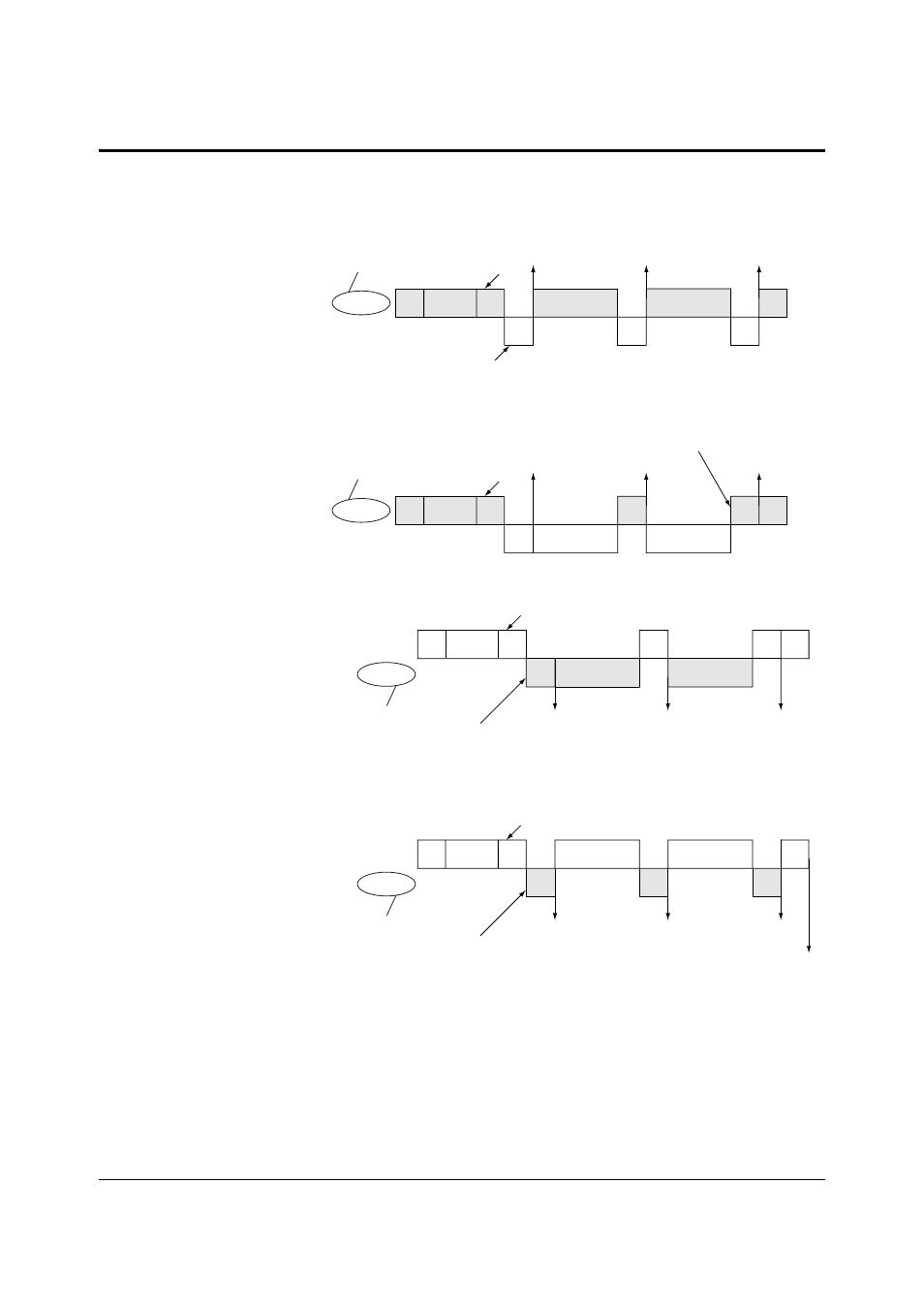

Figure 13-3 shows the MN102H75K/85K operation sequence in each of these

modes. In all modes, the I

2

C bus controller generates an interrupt after each data

byte transfer, then the software loads the next data byte.

A. Master Transmitter

B. Master Receiver

C. Slave Transmitter

D. Slave Receiver

Figure 13-3 I

2

C Bus Interface Operation

Master

S

Address

(7 bits)

R/W

Data (8 bits)

Data (8 bits)

P

Slave

ACK

ACK

ACK

R/W = 0

Interrupt

Interrupt

Interrupt

Normally ACK = 0

MN102H51K

Master

S

Address

(7 bits)

R/W

Data (8 bits)

Data (8 bits)

P

Slave

ACK

ACK

ACK

R/W = 1

Interrupt

Interrupt

Interrupt

ACK = 1 signals transfer

end to slave transmitter.

MN102H51K

Master

S

Address

(7 bits)

R/W

Data (8 bits)

Data (8 bits)

P

Slave

ACK

ACK

ACK

R/W = 1

Interrupt

Interrupt

Interrupt

ACK = 1 signals transfer

end to slave transmitter.

Ack = 0

Ack = 1

When the microcontroller is addressed,

it outputs ACK = 0 and sets the AAS bit

of the I2CDREC register to 1.

MN102H51K

Master

S

Address

(7 bits)

R/W

Data (8 bits)

Data (8 bits)

P

Slave

ACK

ACK

ACK

R/W = 0

Interrupt

Interrupt

Interrupt

STS sets to 1.

Interrupt

When the microcontroller is addressed,

it outputs ACK = 0 and sets the AAS bit

of the I2CDREC register to 1.

MN102H51K