4 general specifications – Lucent Technologies MN10285K User Manual

Page 27

General Description

General Specifications

Panasonic Semiconductor Development Company

MN102H75K/F75K/85K/F85K LSI User Manual

26

Panasonic

1.4

General Specifications

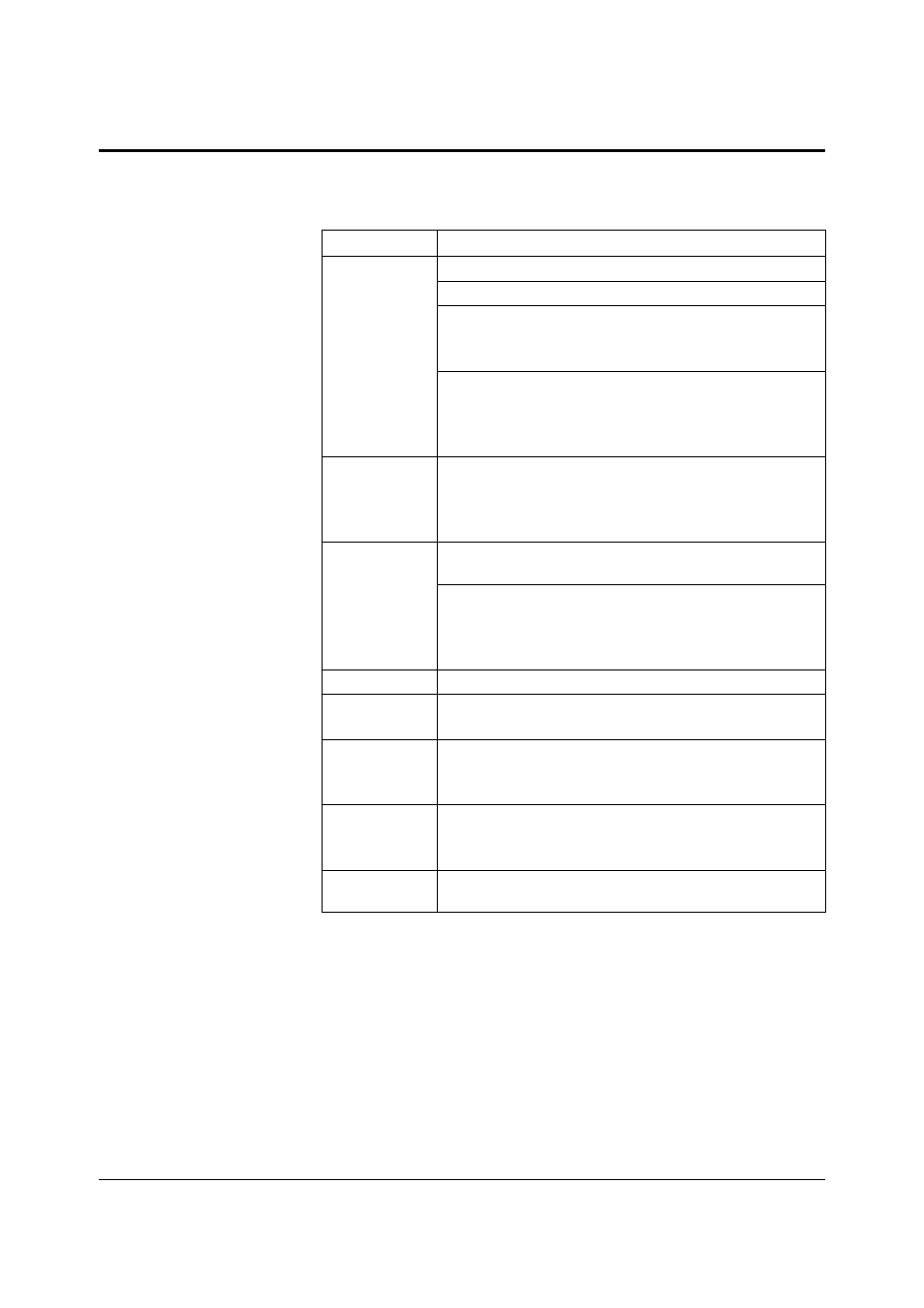

Table 1-1 General Specifications

Parameter

Specification

Structure

Internal multiplier (16-bit × 16-bit = 32-bit) and saturate calculator

Load/store architecture

Eight registers:

♦

Four 24-bit data registers

♦

Four 24-bit address registers

Other:

♦

24-bit program counter

♦

16-bit processor status word

♦

16-bit multiply/divide register

Instruction set

♦

41 instructions

♦

6 addressing modes

♦

1-byte basic instruction length

♦

Code assignment: 1 byte (basic) + 0 to 6 bytes (extension)

Performance

12-MHz internal operating frequency (with a 4-MHz external oscilla-

tor)

Instruction execution clock cycles:

♦

Minimum 1 clock cycle (83.3 ns) for register-to-register operations

♦

Minimum 1 clock cycle (83.3 ns) for load/store operations

♦

Minimum 2 clock cycles (167 ns) for branch operations

Pipeline

3-stage: fetch, decode, execute

Address space

♦

Linear address space

♦

Shared instruction/data space

Interrupts

♦

6 external

♦

30 internal

♦

7 priority level settings

Low-power modes

♦

STOP

♦

HALT

♦

SLOW

Oscillation fre-

quency

4 MHz (48 MHz with internal PLL)