Profibus interface center, Spc3 – Siemens SPC3 User Manual

Page 52

PROFIBUS Interface Center

SPC3

Page 50

V1.3

SPC3 Hardware Description

2003/04

Copyright (C) Siemens AG 2003. All rights reserved.

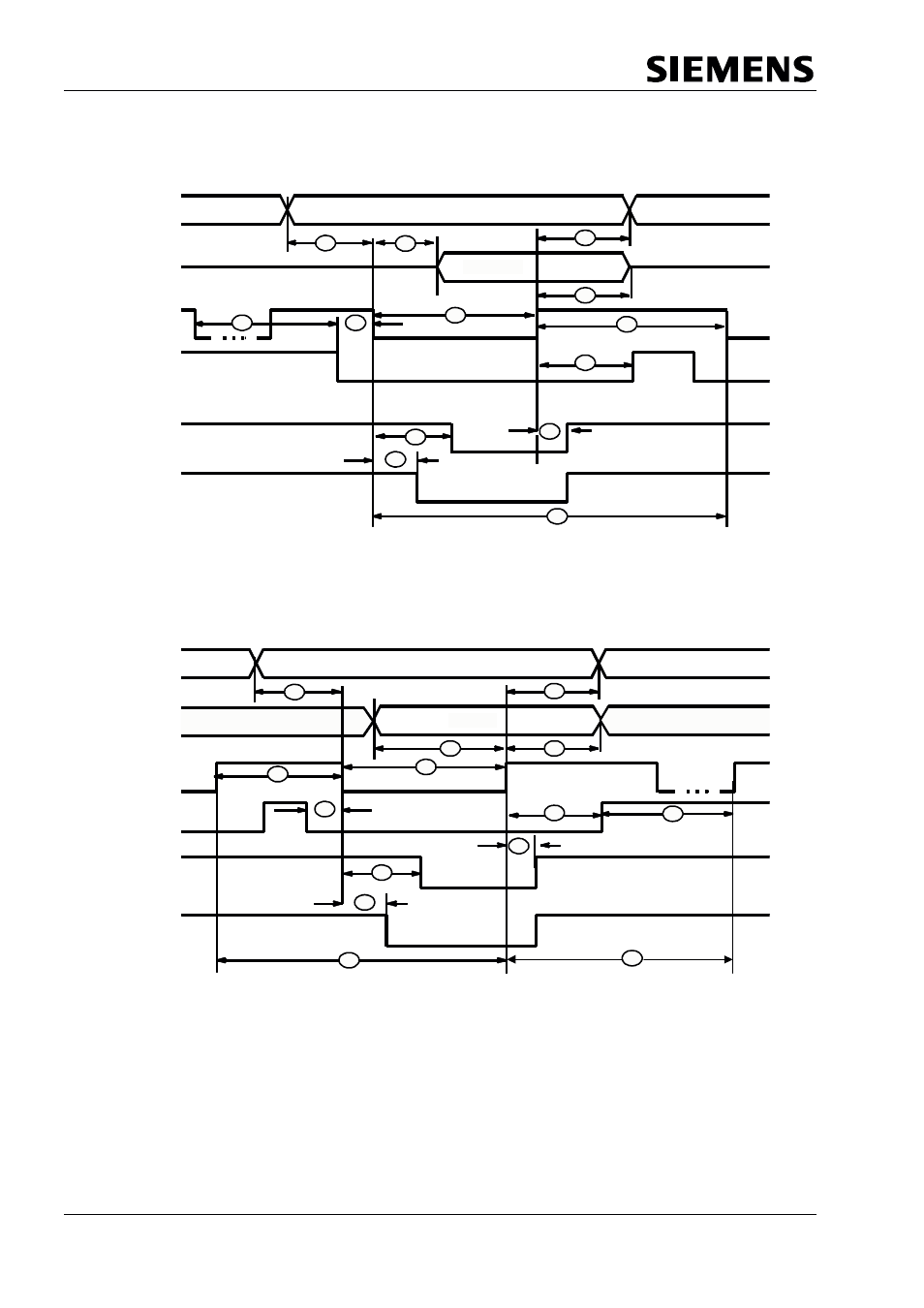

Asynchronous Intel-Mode, Processor-Read-Timing

XRD

VALID

Data Out

AB(10..0)

DB(7..0)

XCS

XWR = log.'1'

23

28

22

25

21

24

XREADY

(normal)

XREADY

(early)

27

30

20

29

26

34

35

Asynchronous Intel-Mode, Processor-Write-Timing

XWR

VALID

AB(10..0)

DB(7..0)

XRD = log.'1'

23

22

32

33

31

Data In

XCS

XREADY

(normal)

27

30

28

20

26

29

34

XREADY

(early)

36

37

8.5.4 Timing in the Synchronous Motorola Mode (E_Clock-Mode, for example, 68HC11) :

For a CPU clockline through the SPC3, the output clock pulse (CLKOUT2/4) must be 4 times larger than the

E_CLOCK. That is, a clock pulse signal must be present at the CLK input that is at least 10 times larger

than the desired system clock pulse (E_CLOCK). The Divider-Pin must be placed on

This results in an E_CLOCK of 3MHz.

- C2-010 (51 pages)

- Simatic M7-400 (638 pages)

- S323 (381 pages)

- CL-010-I (104 pages)

- SIMODRIVE 611-D (1154 pages)

- CL-110 (111 pages)

- ADSL 50 (73 pages)

- S5-135U/155U (560 pages)

- eWON4002 (38 pages)

- SpeedStream 5450 (83 pages)

- 4200 Series (85 pages)

- SL4 (104 pages)

- Simens Gigaset WLAN dsl/cable SE551 (148 pages)

- ADVANCE NETWORK COMMUNICATIONS BOARD/DATANET 2000592-001 (72 pages)

- CL-110-I (129 pages)

- 5890 (102 pages)

- SIMATIC TIWAY 1 (208 pages)

- SS1024 (48 pages)

- SE505 (135 pages)

- GIGASET 54 (56 pages)

- SLI-5310-I IAD (128 pages)

- ProLINE-RoadRunner (58 pages)

- CP 1515 (299 pages)

- Gigaset 3070 (83 pages)

- Terminal TC35 (39 pages)

- SIMATIC PC Adapter TS Adapter (28 pages)

- 108 (143 pages)

- SX763 (156 pages)

- 500 NIM (138 pages)

- Commissioning PC Stations C79000-G8976-C156-07 (300 pages)

- E-110 (90 pages)

- TC65 (90 pages)

- MC35 (228 pages)

- TC35 (39 pages)

- Gigaset SX541 WLAN dsl (187 pages)

- 2614 (44 pages)

- 2602 (32 pages)

- BUSINESS CLASS 5930 (94 pages)

- DTU3005-B (54 pages)

- SpeedStream 2624 (2 pages)

- IEEE802.11 (84 pages)

- SANTIS-ab (28 pages)

- gigaset SE551 (175 pages)

- 300 (56 pages)