Profibus interface center, Spc3, 3 interrupt controller – Siemens SPC3 User Manual

Page 24

PROFIBUS Interface Center

SPC3

Page 22

V1.3

SPC3 Hardware Description

2003/04

Copyright (C) Siemens AG 2003. All rights reserved.

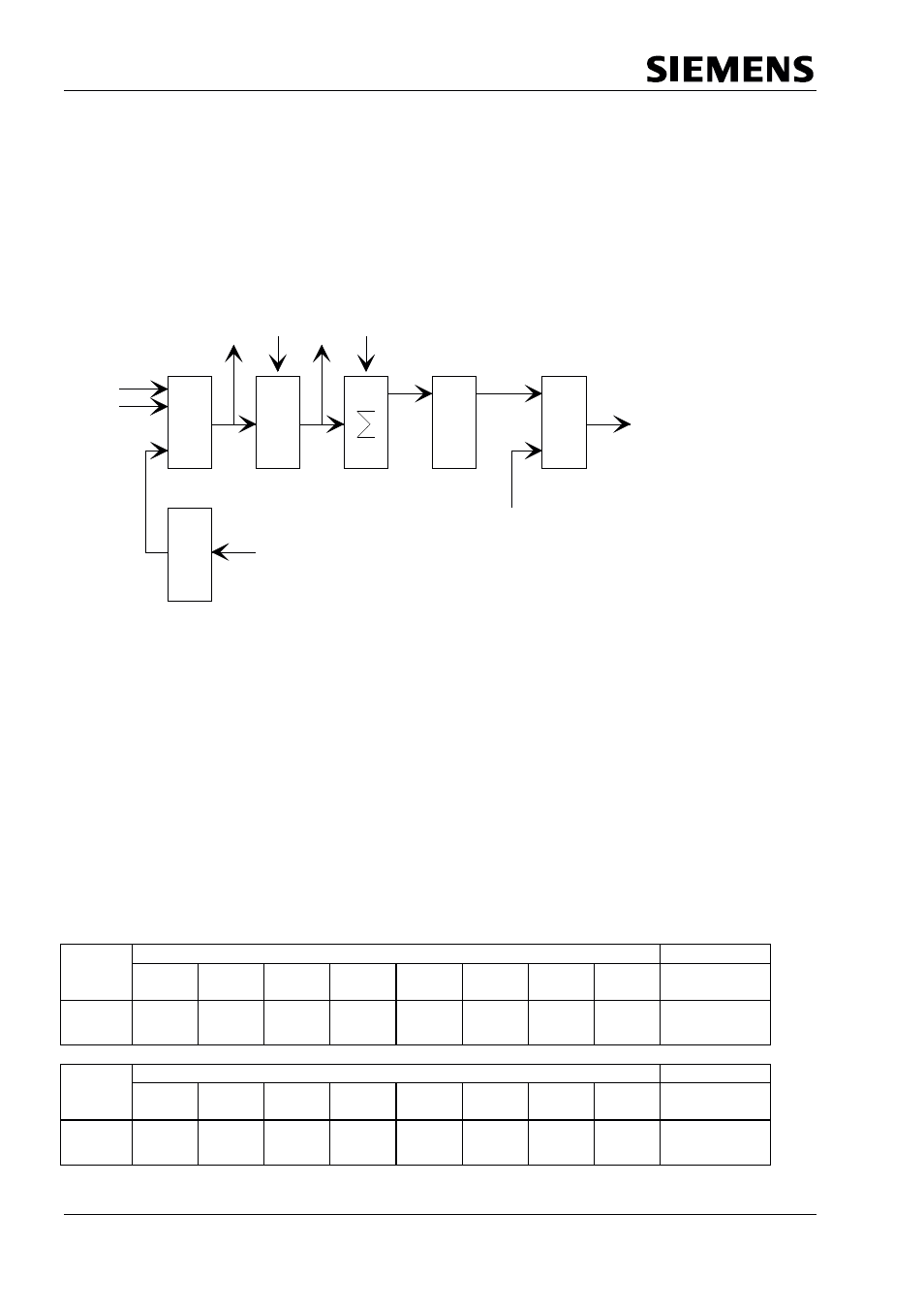

5.3 Interrupt Controller

The processor is informed about indication messages and various error events via the interrupt controller.

Up to a total of 16 events are stored in the interrupt controller. The events are carried out on an interrupt

output. The controller does not have a prioritization level and does not provide an interrupt vector (not

8259A compatible!).

The controller consists of an Interrupt Request Register (IRR), an Interrupt Mask Register (IMR), an Interrupt

Register (IR), and an Interrupt Acknowledge Register (IAR).

IRR

IMR

IAR

S

R

FF

S

R

SPC3

uP

uP

uP

uP

uP

uP

INT_Pol

SEP_INT

IR

X/INT

Each event is stored in the IRR. Individual events can be suppressed via the IMR. The input in the IRR is

independent of the interrupt masks. Event signals not masked out in the IMR generate the X/INT interrupt

via a sum network. The user can set each event in the IRR for debugging.

Each interrupt event the processor processed must be deleted via the IAR (except for New_Prm_Data,

New_DDB_Prm_Data, and New_Cfg_Data). Log ‘1’ must be written on the relevant bit position. If a new

event and an acknowledge from the previous event are present at the IRR at the same time, the event

remains stored. If the processor subsequently enables a mask, it must be ensured that no prior input is

present in the IRR. For safety purposes, the position in the IRR must be deleted prior to the mask enable.

Prior to exiting the interrupt routine, the processor must set the “end of interrupt signal (E01) = 1” in the

mode register. The interrupt cable is switched to inactive with this edge change. If another event must be

stored, the interrupt output is not activated again until after an interrupt inactive time of at least 1 usec or 1-

2 ms. This interrupt inactive time can be set via ‘EOI_Timebase.’ This makes it possible to again come into

the interrupt routine when an edge-triggered interrupt input is used.

The polarity for the interrupt output is parameterized via the INT_Pol mode bit. After the hardware reset,

the output is low-active.

Address

Bit Position

Designation

Control

Register

7

6

5

4

3

2

1

0

00H

(Intel)

Res

Res

Res

User_

Timer_

Clock

WD_DP_

Mode_

Timeout

Baud_

rate_

Detect

Go/Leave

Data_

EX

MAC_

Reset

Int-Req-Reg

7..0

Address

Bit Position

Designation

Control

Register

15

14

13

12

11

10

9

8

01H

(Intel)

Res

Res

DX_OUT

Diag_

Puffer_

Changed

New_

Prm_

Data

New_

Cfg_

Data

New_

SSA_

Data

New_GC

Com

mand

Int-Req-Reg 7

15..8