Spc3 profibus interface center – Siemens SPC3 User Manual

Page 13

SPC3

PROFIBUS Interface Center

SPC3 Hardware Description

V1.3

Page 11

Copyright (C) Siemens AG 2003 All rights reserved.

2003/04

4 Memory Allocation

4.1 Memory Area Distribution in the SPC3

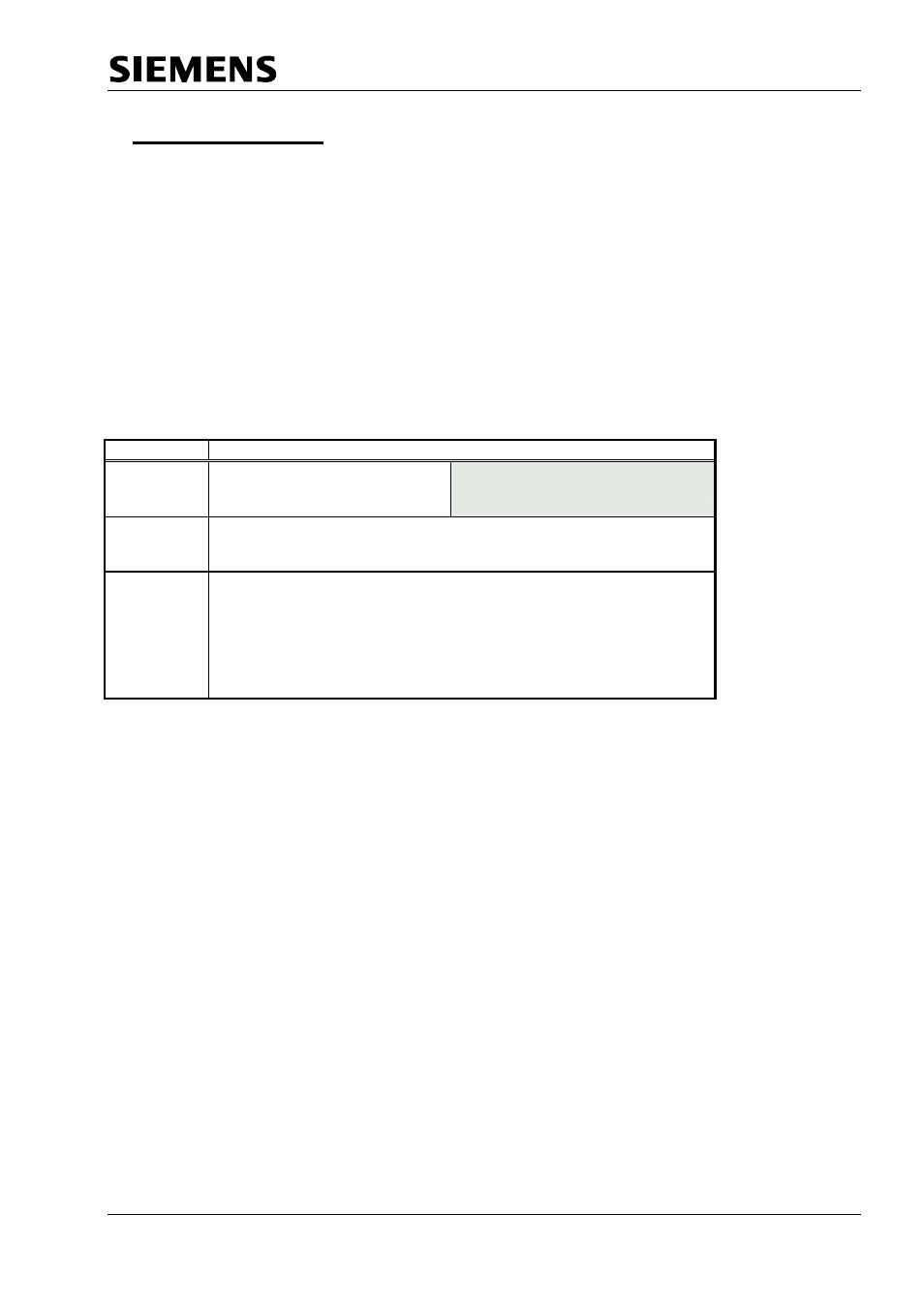

The figure displays the division of the SPC3 1.5k internal address area.

The internal latches/register are located in the first 21 addresses. The internal latches/register either come

from the controller or influence the controller. Certain cells can be only read or written. The internal work

cells to which the user has no access are located in RAM at the same addresses.

The organizational parameters are located in RAM beginning with address 16H. The entire buffer structure

(for the DP-SAPS) is written based on these parameters. In addition, general parameter setting data

(station address, Ident no., etc.) are transferred in these cells and the status displays are stored in these

cells (global control command, etc.).

Corresponding to the parameter setting of the organizational parameters, the user-generated buffers are

located beginning with address 40H. All buffers or lists must begin at segment addresses (48 bytes

segmentation).

Address

Function

000H

Processor parameters

internal work cells

Latches/register

(22 bytes)

016H

Organizational

parameters

(42 bytes)

040H

DP- buffer:

Data In (3) *

Data Out (3) *

Diagnostics (2)

Parameter setting data (1)

5FFH

Configuration data (2)

Auxiliary buffer (2)

SSA-buffer(1)

Figure 4.1: SPC3 Memory Area Distribution

Caution:

The HW prohibits overranging the address area. That is, if a user writes or reads past the memory

end, 400H is subtracted from this address and the user therefore accesses a new address. This

prohibits overwriting a process parameter. In this case, the SPC3 generates the RAM access

violation interrupt. If the MS overranges the memory end due to a faulty buffer initialization, the

same procedure is executed.

* Data In is the input data from PROFIBUS slave to master

Data out is the output data from PROFIBUS master to slave