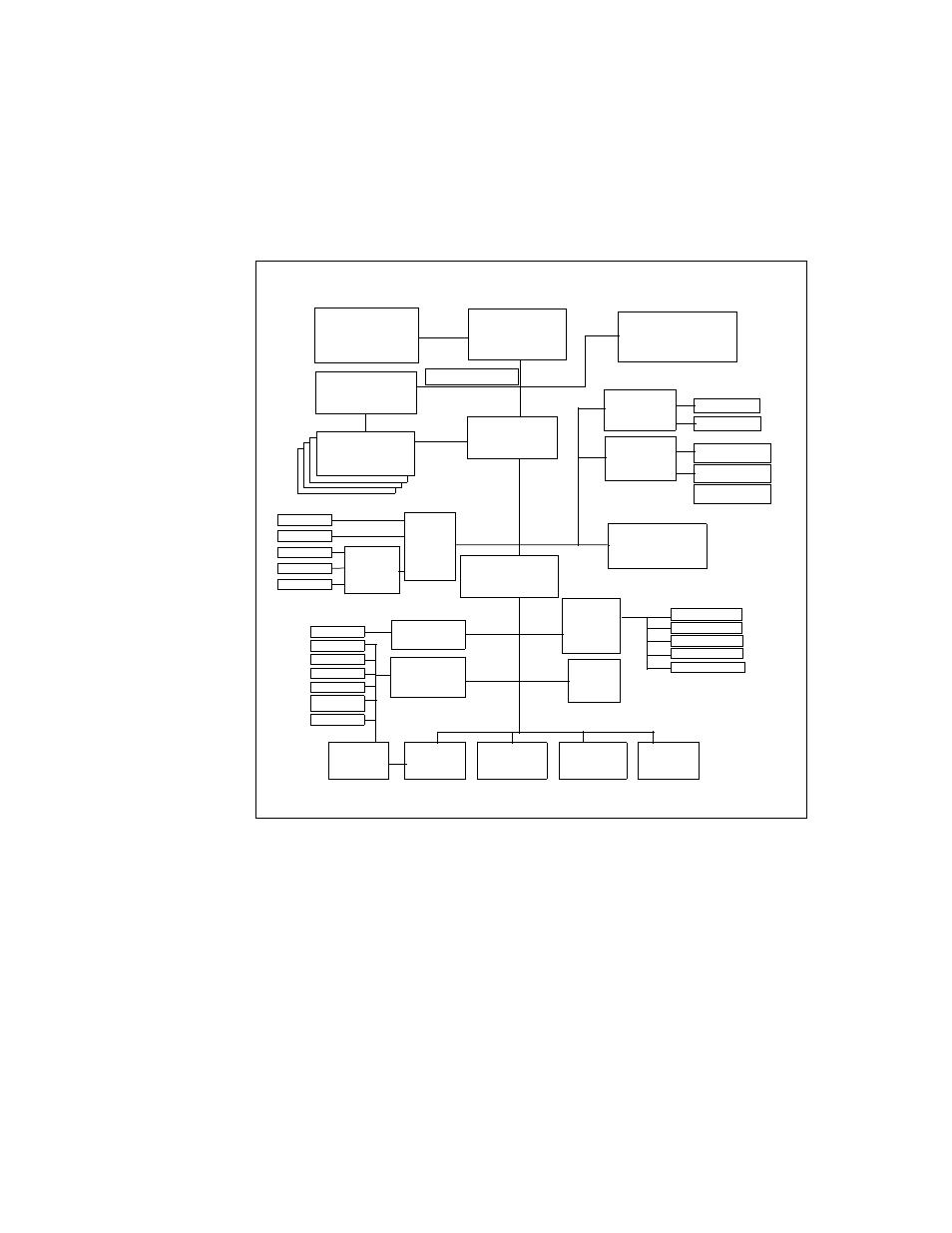

Planar block diagram of the rs/6000 model 150 – IBM HANDBOOK 260 User Manual

Page 45

Hardware Overview

27

parity-checked synchronous L2 cache. The Model 150 also features an

enhanced memory controller that uses ECC SDRAM memory.

The local system bus on the RS/6000 Model 150 is a 60X bus running at 83

MHz. This bus is 64 bits wide (with an additional 8 bits for parity) and is

synchronous. The processor clock and regulator card reside as one unit,

namely the OVdd/Vdd/PLL card. This is illustrated in the planar design of the

Model 150 in Figure 8.

Figure 8. Planar Block Diagram of the RS/6000 Model 150

In the Model 150, the 60X bus runs from the PowerPC 604e processor and

connects to an enhanced memory controller chip, which has a processor

Integrated 1 MB

Parity L2 Cache

IPGA

604e-375 MHz

OVdd/Vdd/PLL

IBM

Card

Ctrl/Buffer

ECC

PCIB/MC

ECC SDRAM

DIMM

100/10

Ethernet

Ultra SCSI

Enet RJ45

Enet AUI

Local bus 83 MHz

Int Ultra SCSI

Repeater

Ext Ultra SCSI

RISER

PCI/PCI

Bridge &

Clock

Drivers

Tablet

Parallel

Serial 1

Serial 2

Floppy

Keyboard

Mouse

National

PC87308

National

Secondary

Business

Audio

IBM MPIC

Controller

Headphone

Speaker

Line Out

Line In

Microphone

1 MB

Flash

ROM

32 KB

NVRAM

Logic

Front Panel

Controller

Enhanced

Security

Power

Mgmt

PCI

Bu

s

3

3

M

H

z

ISA Bu

s

8 M

H

z

PCI-to-ISA

Bridge

Unit

UART 16550

PCI Bridge

PCI Slot 1

PCI Slot 4

PCI Slot 5

PCI Slot 2

PCI Slot 3