Memory address, Chapter 3 macsi host interface, Introduction – Interphase Tech CONDOR 4221 User Manual

Page 65: Typographic convention

53

CHAPTER 3

MACSI HOST INTERFACE

Introduction

This chapter defines the MACSI host interface for the Interphase V/Ethernet 4221 Condor. The Condor and its MACSI

host interface are designed to be backwards compatible with the Interphase V/Ethernet 4207 Eagle MACSI host

interface. This compatibility exists to the extent that single port operation can be accomplished with virtually no

alterations to an existing Eagle driver, and full 4 port operation can be provided with minimal changes

This interface provides support for:

•

Offboard IOPBs, located in host memory

•

Offboard postback of completed commands

•

Multiple command completions

•

Offboard postback of network statistics

Typographic Convention

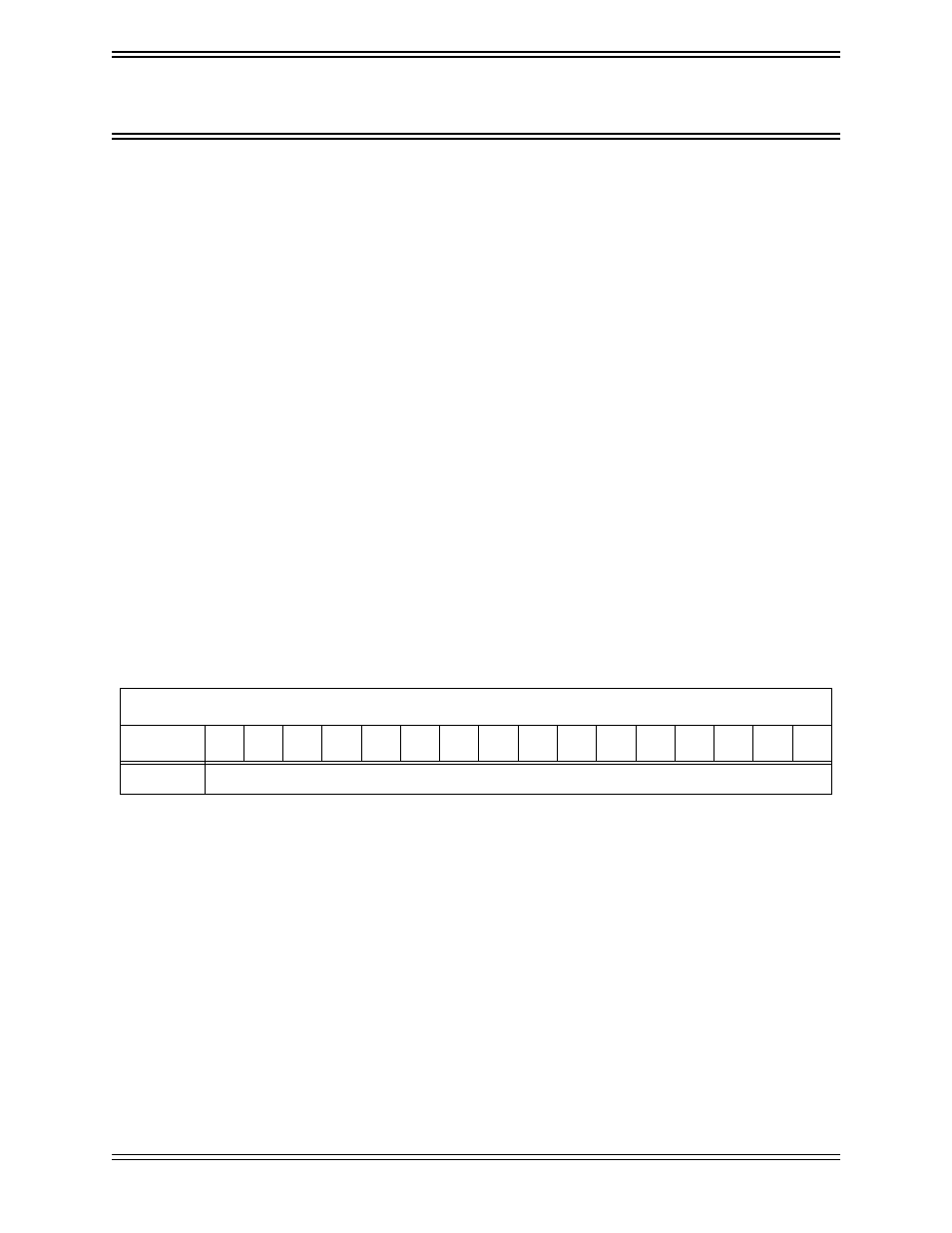

When defining the layout of commands and the shared memory interface between the host and the Condor controller,

three different conventions are used to specify the field offset:

Memory Address

The value in the far left column specifies an offset in bytes from the beginning of the Short I/O shared memory

space, as follows:

This is indicated by the term Addr appearing in the heading block of the table.

Command Response Block

Addr

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x730

Command Response Status Word (CRSW)