1 automatic alarm generation, 6 per-channel loopback, Automatic alarm generation – Maxim Integrated DS33R11 User Manual

Page 77: Hannel, Oopback, Table 10-4. e1 alarm criteria

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

77 of 344

10.5.1 Automatic Alarm Generation

The device can be programmed to automatically transmit AIS or remote alarm. When automatic AIS generation is

enabled (TR.E1TCR2.1 = 1), the device monitors the receive-side framer to determine if any of the following

conditions are present: loss-of-receive frame synchronization, AIS alarm (all ones) reception, or loss-of-receive

carrier (or signal). The framer forces either an AIS or remote alarm if any one or more of these conditions is

present.

When automatic RAI generation is enabled (TR.E1TCR2.0 = 1), the framer monitors the receive side to determine

if any of the following conditions are present: loss-of-receive-frame synchronization, AIS alarm (all ones) reception,

loss-of-receive carrier (or signal), or if CRC4 multiframe synchronization cannot be found within 128ms of FAS

synchronization (if CRC4 is enabled). If any one or more of these conditions is present, then the framer transmits

an RAI alarm. RAI generation conforms to ETS 300 011 specifications and a constant remote alarm is transmitted

if the device cannot find CRC4 multiframe synchronization within 400ms as per G.706.

Note: It is an invalid state to have both automatic AIS generation and automatic remote alarm generation enabled

at the same time.

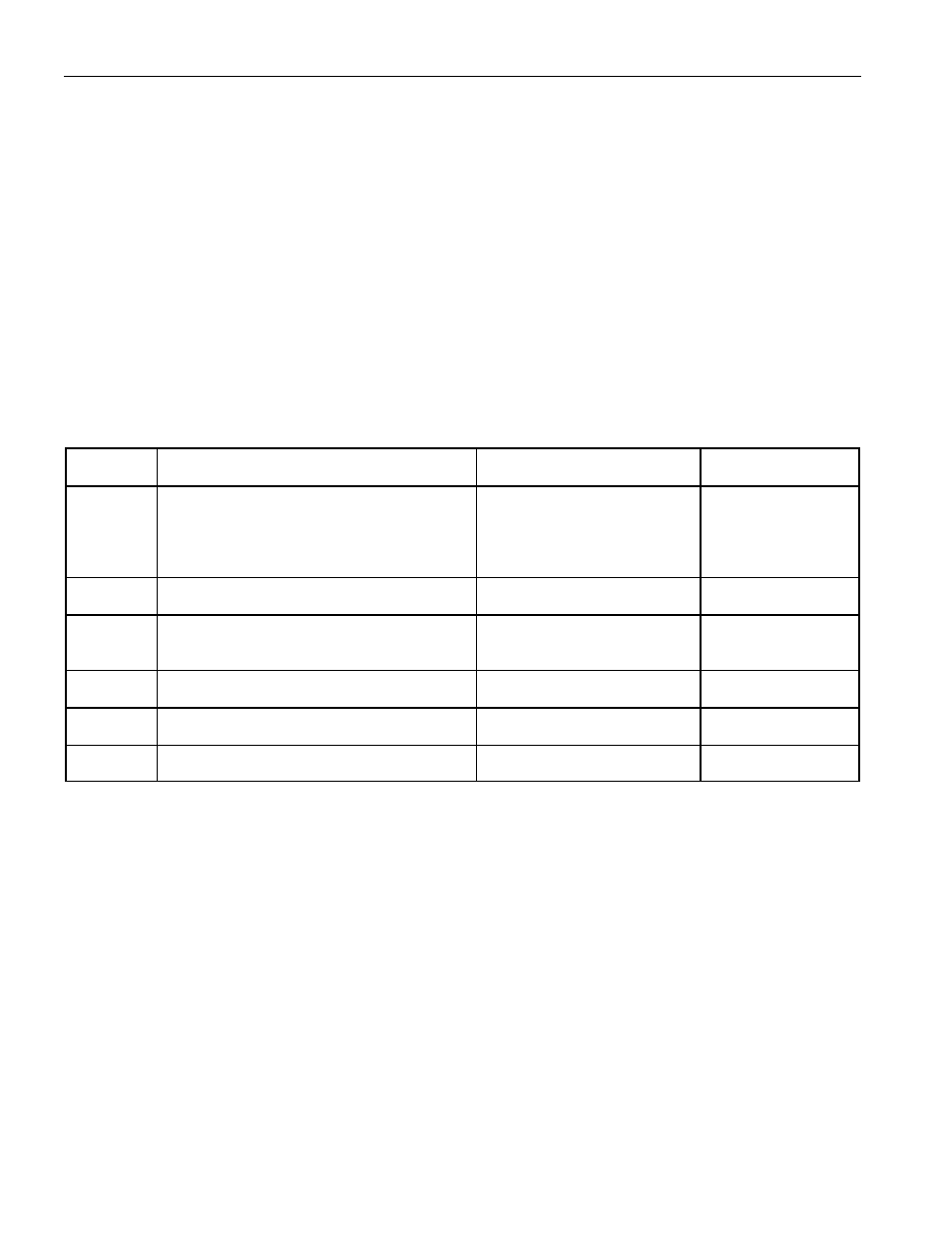

Table 10-4. E1 Alarm Criteria

ALARM SET

CRITERIA CLEAR

CRITERIA

ITU

SPECIFICATION

RLOS

An RLOS condition exists on power-up

prior to initial synchronization, when a

resync criteria has been met, or when a

manual resync has been initiated by

TR.E1RCR1.0

RCL

255 or 2048 consecutive 0s received as

determined by TR.E1RCR2.0

At least 32 1s in 255-bit times

are received

G.775/G.962

RRA

Bit 3 of nonalign frame set to 1 for three

consecutive occasions

Bit 3 of nonalign frame set to

0 for three consecutive

occasions

O.162

2.1.4

RUA1

Fewer than three 0s in two frames (512

bits)

More than two 0s in two

frames (512 bits)

O.162

1.6.1.2

RDMA

Bit 6 of time slot 16 in frame 0 has been set

for two consecutive multiframes

V52LNK

Two out of three Sa7 bits are 0

G.965

10.6 Per-Channel Loopback

The per-channel loopback registers (PCLRs) determine which channels (if any) from the backplane should be

replaced with the data from the receive side or, i.e., off of the T1 or E1 line. If this loopback is enabled, then

transmit and receive clocks and frame syncs must be synchronized. One method to accomplish this is to connect

RCLKO to TCLKT and RFSYNC to TSYNC. There are no restrictions on which channels can be looped back or on

how many channels can be looped back.

Each of the bit positions in the per-channel loopback registers (TR.PCLR1/TR.PCLR2/TR.PCLR3/TR.PCLR4)

represents a DS0 channel in the outgoing frame. When these bits are set to a 1, data from the corresponding

receive channel replaces the data on TSERI for that channel.