Maxim Integrated DS33R11 User Manual

Page 36

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

36 of 344

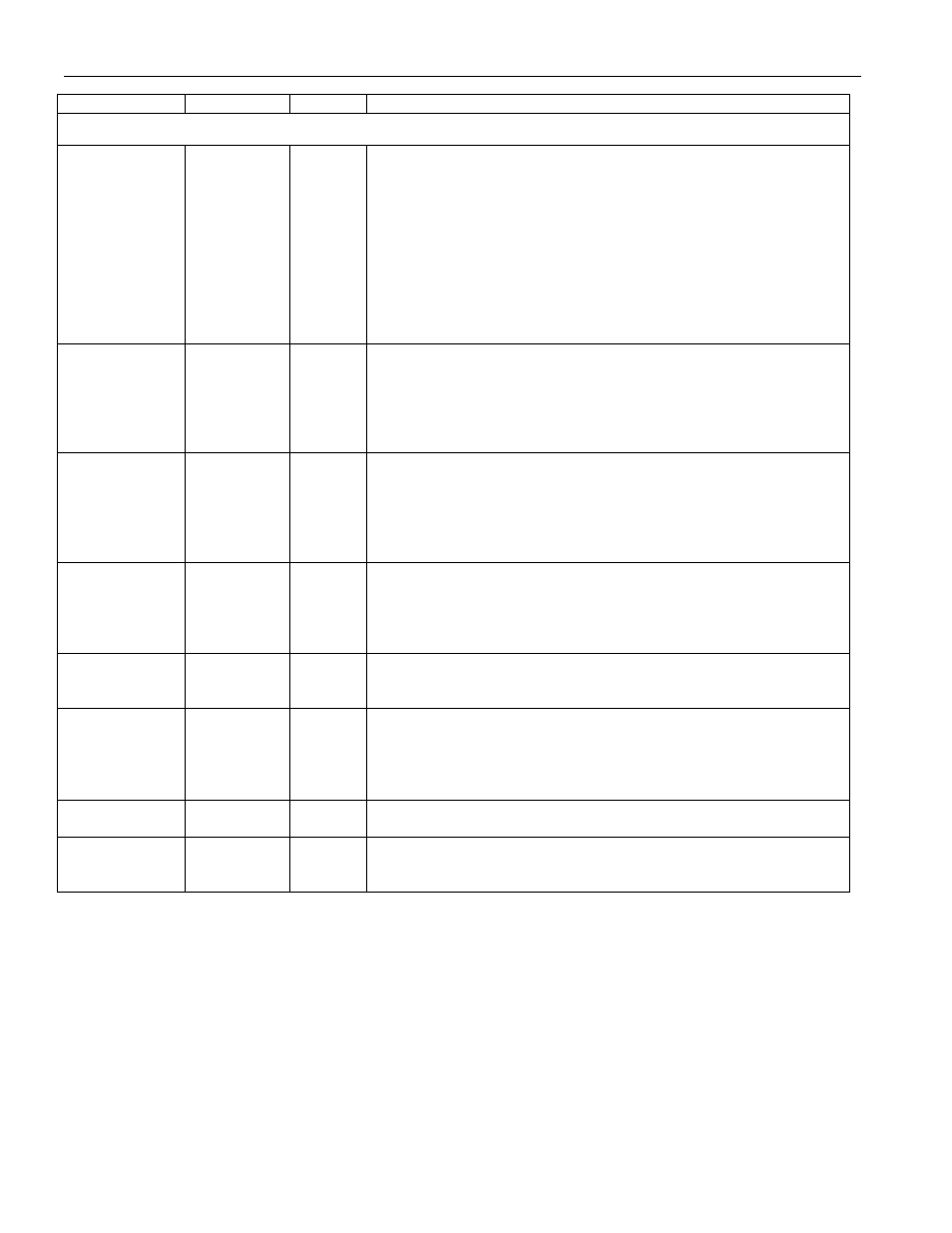

NAME PIN

TYPE

FUNCTION

HARDWARE AND STATUS PINS

LIUC B2

I

Line Interface Unit Connect: When a logic low is present on this

input pin, the T1/E1/J1 Framer and LIU are not internally

connected. The line interface circuitry will be separated from the

framer/formatter circuitry and the TPOSI, TNEGI, TDCLKI, RPOSI,

RNEGI, and RDCLKI input pins will be active.

When a logic high is present on this input pin, the T1/E1/J1 Framer

is internally connected to the LIU. The TPOSI, TNEGI, TDCLKI,

RPOSI, RNEGI, RDCLKI input pins are deactivated. When LIUC is

connected high, the TPOSI, TNEGI, TDCLKI, RPOSI, RNEGI, and

RDCLKI pins should be tied low.

RST

A8 I

Reset for the Ethernet Mapper: An active low signal on this pin

resets the internal registers and logic of the protocol conversion

device. This pin should remain low until power, SYSCLKI, RX_CLK,

and TX_CLK are stable, then set high for normal operation. This

input requires a clean edge with a rise time of 25ns or less to

properly reset the device.

TSTRST C4 I

Test/Reset for the T1/E1/J1 Transceiver: A dual-function pin. A

zero-to-one transition issues a hardware reset to the transceiver

register set. A reset clears all configuration registers. Configuration

register contents are set to zero. Leaving TSTRST high will tri-state

all output and I/O pins (including the parallel control port). Set low

for normal operation. Useful in board-level testing.

MODEC[0],

MODEC[1]

B19,

B20

I

Mode Control for Processor Interface:

00 = Read/Write Strobe Used (Intel Mode)

01 = Data Strobe Used (Motorola Mode)

10 = Reserved. Do not use.

11 = Reserved. Do not use.

QOVF H18

O

Queue Overflow for Ethernet Mapper: This pin goes high when

the transmit or receive queue has overflowed. This pin will go low

when the high watermark is reached again.

RLOS/LTC N1 O

T1/E1/J1 Receive Loss-of-Sync/Loss-of-Transmit Clock: A dual

function output that is controlled by the CCR1.0 control bit. This pin

can be programmed to either toggle high when the synchronizer is

searching for the frame and multiframe or to toggle high if the

TCLKT pin has not been toggled for 5

μs.

RCL B5

O

T1/E1/J1 Receive Carrier Loss: Set high when the T1/E1/J1 line

interface detects a carrier loss.

RSIGF P3 O

T1/E1/J1 Receive Signaling-Freeze Output: Set high when the

signaling data is frozen by either automatic or manual intervention.

Used to alert downstream equipment of the condition.