Maxim Integrated DS33R11 User Manual

Page 226

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

226 of 344

Register Name:

TR.IMR6, TR.IMR7

Register Description:

HDLC # 1 Interrupt Mask Register 6

HDLC # 2 Interrupt Mask Register 7

Register Address:

21h, 23h

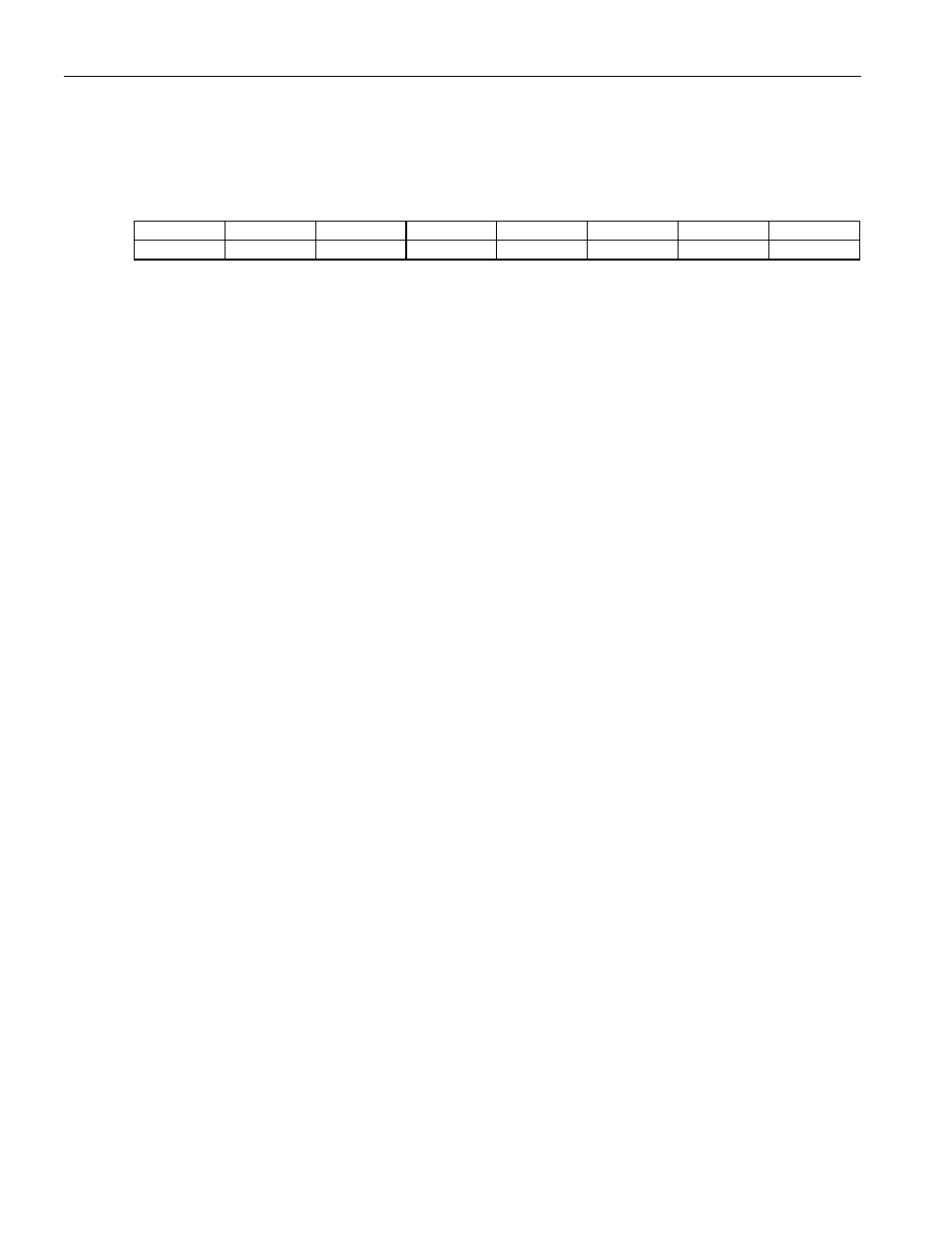

Bit

# 7 6 5 4 3 2 1 0

Name —

TMEND

RPE RPS

RHWM

RNE

TLWM

TNF

Default

0 0 0 0 0 0 0 0

Bit 6: Transmit Message-End Event (TMEND)

0 = interrupt masked

1 = interrupt enabled

Bit 5: Receive Packet-End Event (RPE)

0 = interrupt masked

1 = interrupt enabled

Bit 4: Receive Packet-Start Event (RPS)

0 = interrupt masked

1 = interrupt enabled

Bit 3: Receive FIFO Above High-Watermark Condition (RHWM)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only

Bit 2: Receive FIFO Not Empty Condition (RNE)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only

Bit 1: Transmit FIFO Below Low-Watermark Condition (TLWM)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only

Bit 0: Transmit FIFO Not Full Condition (TNF)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only