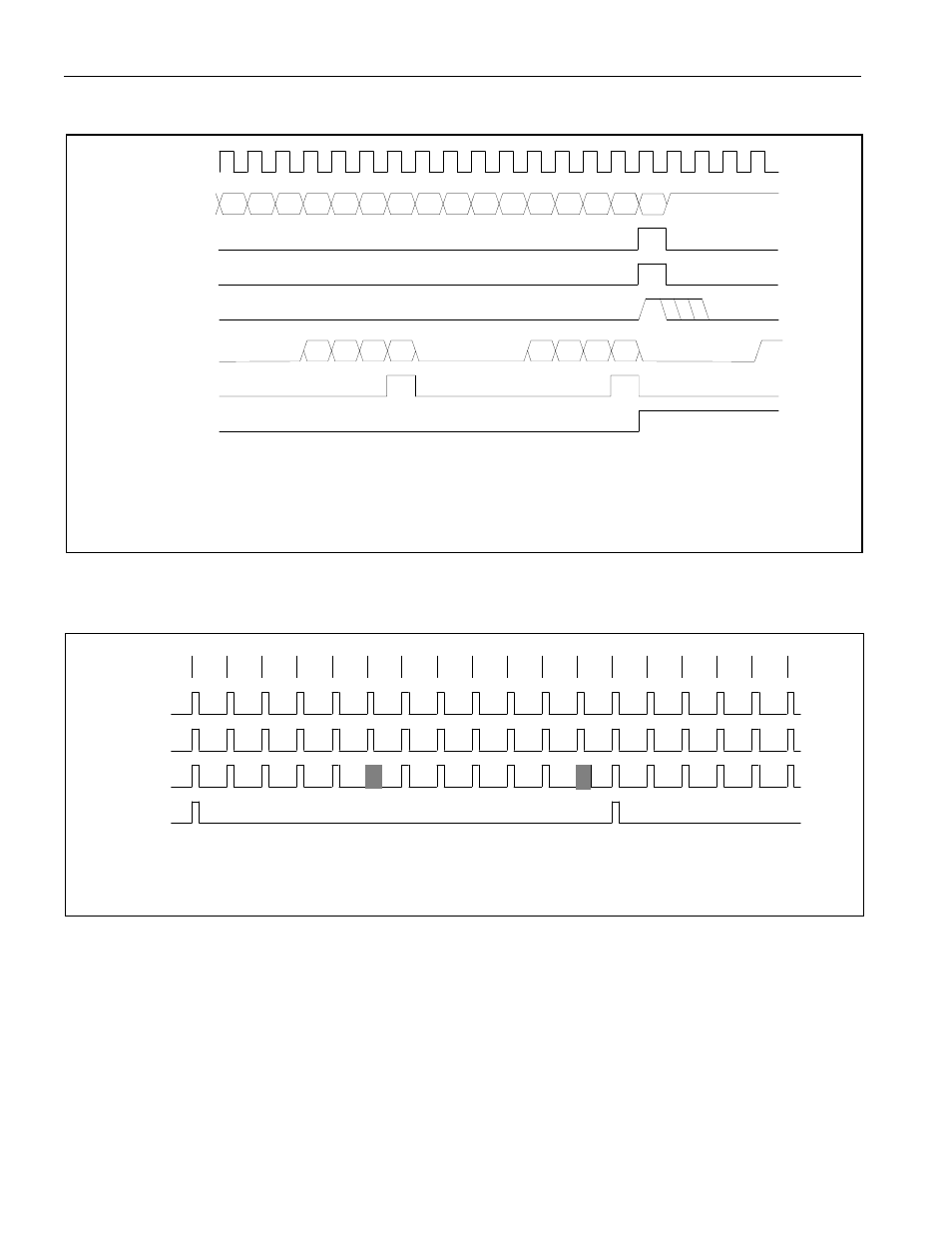

Figure 12-15. transmit-side d4 timing – Maxim Integrated DS33R11 User Manual

Page 305

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

305 of 344

Figure 12-14. Receive-Side 2.048MHz Boundary Timing (Elastic Store Enabled)

RSER O

CHANNEL 1

RCHCLK

RCHBLK

RSYSCLK

RSYNC

CHANNEL 31

CHANNEL 32

1

3

4

RSYNC

2

RMSYNC

RSIG

CHANNEL 31

CHANNEL 32

B

A

C/A D/B

C/A D/B

A

B

CHANNEL 1

LSB MSB

LSB

F

5

NOTE 1: RSERO DATA IN CHANNELS 1, 5, 9, 13, 17, 21, 25, AND 29 ARE FORCED TO 1.

NOTE 2: RSYNC IS IN THE OUTPUT MODE (TR.IOCR1.4 = 0).

NOTE 3: RSYNC IS IN THE INPUT MODE (TR.IOCR1.4 = 1).

NOTE 4: RCHBLK IS FORCED TO 1 IN THE SAME CHANNELS AS RSERO (SEE NOTE 1).

NOTE 5: THE F-BIT POSITION IS PASSED THROUGH THE RECEIVE-SIDE ELASTIC STORE.

Figure 12-15. Transmit-Side D4 Timing

1

2

3

4

5

6

7

8

9

10

11 12

1

2

3

4

5

1

2

3

TSSYNC

FRAME#

TSYNC

TSYNC

TSYNC

NOTE 1: TSYNC IN THE FRAME MODE (TR.IOCR1.2 = 0) AND DOUBLE-WIDE FRAME SYNC IS NOT ENABLED (TR.IOCR1.1 = 0).

NOTE 2: TSYNC IN THE FRAME MODE (TR.IOCR1.2 = 0) AND DOUBLE-WIDE FRAME SYNC IS ENABLED (TR.IOCR1.1 = 1).

NOTE 3: TSYNC IN THE MULTIFRAME MODE (TR.IOCR1.2 = 1).