Chapter 3, Motherboard information – Lanner FX-3210 User Manual

Page 23

18

Motherboard Information

Network Application Platforms

Chapter 3

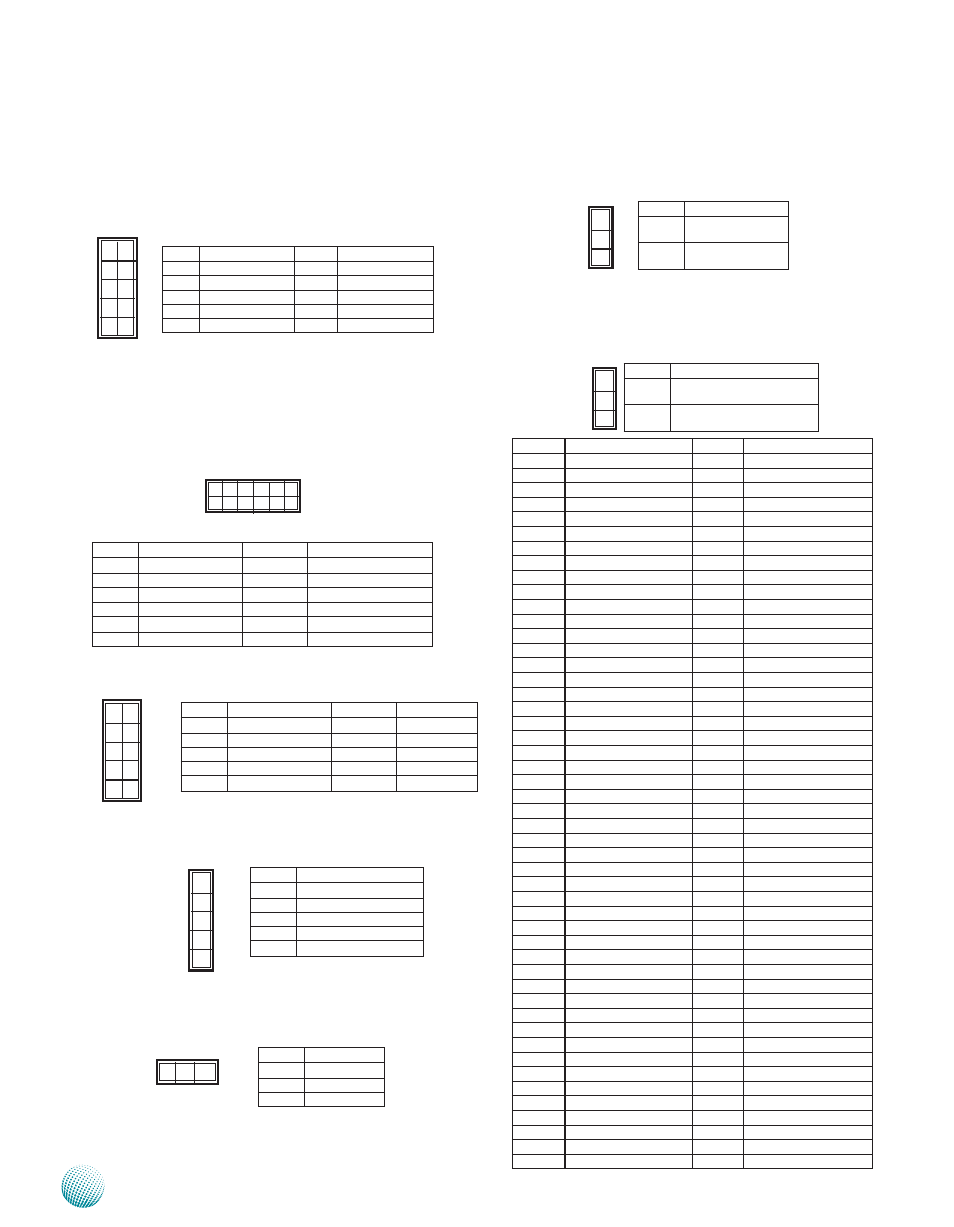

SPI-ROM Update Connector (SPI-ROM1): Using the

appropriate cable to connect this 10-pin ISP in header

connector, the user can update the SPI Flash soldered

on board.

VGA Interface (VGAA1): It is for connecting the VGA

interface cable (2X6 pin to female DB15 connector)

USB and COM Interface signal for LCM card (J29)

Pin Header for Power Management Port (J28)

Case Open Signal (CONN2)

Pin No.

Function

Pin NO.

Function

1

SPI_HD1_N

2

PCH_SPI_CS1_N

3

SPI_CS0

4

V_3P3_SPI

5

SPI_ICH_MISO_R

6

SPI_HOLD0_L

7

NC

8

SPI_ICH_CLK_R

9

Ground

10

SPI_ICH_MOSI_R

2

4

6

8

10

1

3

5

7

9

2 4 6 8 1 0

1 3 5 7 9

Pin No.

Function

PIN NO.

Function

1

R

2

Ground

3

G

4

Ground

5

B

6

Ground

7

H-SYNC

8

NC

9

V-SYNC

10

Ground

11

Detect-display Data

12

Deteck-display CLOCK

9

7

5

3

1

10

8

6

4

2

Pin No.

Function

PIN NO.

Function

1

P5V_DUAL

2

P5V

3

USB-

4

NC

5

USB+

6

HDD_LED-

7

GND

8

GND

9

NXP_TXD

10

NXP_RXD

1

2

3

4

5

Pin No.

Function

1

PSUMAN_SMBCLK

2

NC

3

GND

4

PSUMAN_SMBDATA

5

P5V

PCIe mode selection for PCIe expansion integrated directly

into the CPU (PCIEC1 and CPIEC2):J31

PCIe signal order selection (J32): PCIe signal order selection

for PCIe expansion integrated directly into the CPU:

PCIEC1, PCIEC2, and PCIEC3

PCIEC1/PCIEC2

Pin No.

Function

1-2

The PCIE signal in reverse

order (default)

2-3

The PCIE signal in positive

order

1

2

3

1

2

3

Pin No.

Function

1-2

CPU PCIE divide to

X8,X4,X4

2-3

CPU PCIE divide to

2 PCIEx8 (default)

PIN NO.

FUNCTION

PIN NO.

FUNCTION

B1

+12V

A1

PRSNT1#

B2

+12V

A2

+12V

B3

+12V

A3

+12V

B4

GND

A4

GND

B5

SMCLK

A5

JTAG2

B6

SMDAT

A6

JTAG3

B7

GND

A7

JTAG4

B8

+3.3V

A8

JTAG5

B9

JTAG1

A9

+3.3V

B10

3.3VAUX

A10

+3.3V

B11

WAKE#

A11

PERST#

B12

BYPASS0 Mode

A12

GND

B13

GND

A13

REFCLKA+

B14

CPUPETP0/CPUPETP8

A14

REFCLKA-

B15

CPUPETN0/CPUPETN8

A15

GND

B16

GND

A16

CPUPERP0/CPUPERP8

B17

LANM0_LATCH_H

A17

CPUPERN0/CPUPERN8

B18

GND

A18

GND

B19

CPUPETP1/CPUPETP9

A19

BYPASS1 Mode

B20

CPUPETN1/CPUPETN9

A20

GND

B21

GND

A21

CPUPERP1/CPUPERP9

B22

GND

A22

CPUPERN1/CPUPERN9

B23

CPUPETP2/CPUPETP10

A23

GND

B24

CPUPETN2/CPUPETN10

A24

GND

B25

GND

A25

CPUPERP2/CPUPERP10

B26

GND

A26

CPUPERN2/CPUPERN10

B27

CPUPETP3/CPUPETP11

A27

GND

B28

CPUPETN3/CPUPETN11

A28

GND

B29

GND

A29

CPUPERP3/CPUPERP11

B30

REFCLK1A+

A30

CPUPERN3/CPUPERN11

B31

REFCLK1A-

A31

GND

B32

GND

A32

LANM1_LATCH_H

B33

CPUPETP4/CPUPETP12

A33

LANM1_LATCH_L

B34

CPUPETH4/CPUPETH12

A34

GND

B35

GND

A35

CPUPERP4/CPUPERP12

B36

GND

A36

CPUPERN4/CPUPERN12

B37

CPUPETP5/CPUPETP13

A37

GND

B38

CPUPETN5/CPUPETN13

A38

GND

B39

GND

A39

CPUPERP5/CPUPERP13

B40

GND

A40

CPUPERN5/CPUPERN13

B41

CPUPETP6/CPUPETP14

A41

GND

B42

CPUPETN6/CPUPETN14

A42

GND

B43

GND

A43

CPUPERP6/CPUPERP14

B44

GND

A44

CPUPERN6/CPUPERN14

B45

CPUPETP7/CPUPETP15

A45

GND

B46

CPUPETN7/CPUPETN15

A46

GND

B47

GND

A47

CPUPERP7/CPUPERP15

B48

LANM0_LATCH_L

A48

CPUPERN7/CPUPERN15

B49

GND

A49

GND

Pin No.

Function

1

GND

2

CASE OPEN

3

GND

3 2 1