S1c6200 core cpu, Memory map, Registers – Epson S5U1C62000A User Manual

Page 234: Quick reference for development, S1c62 family assembler package

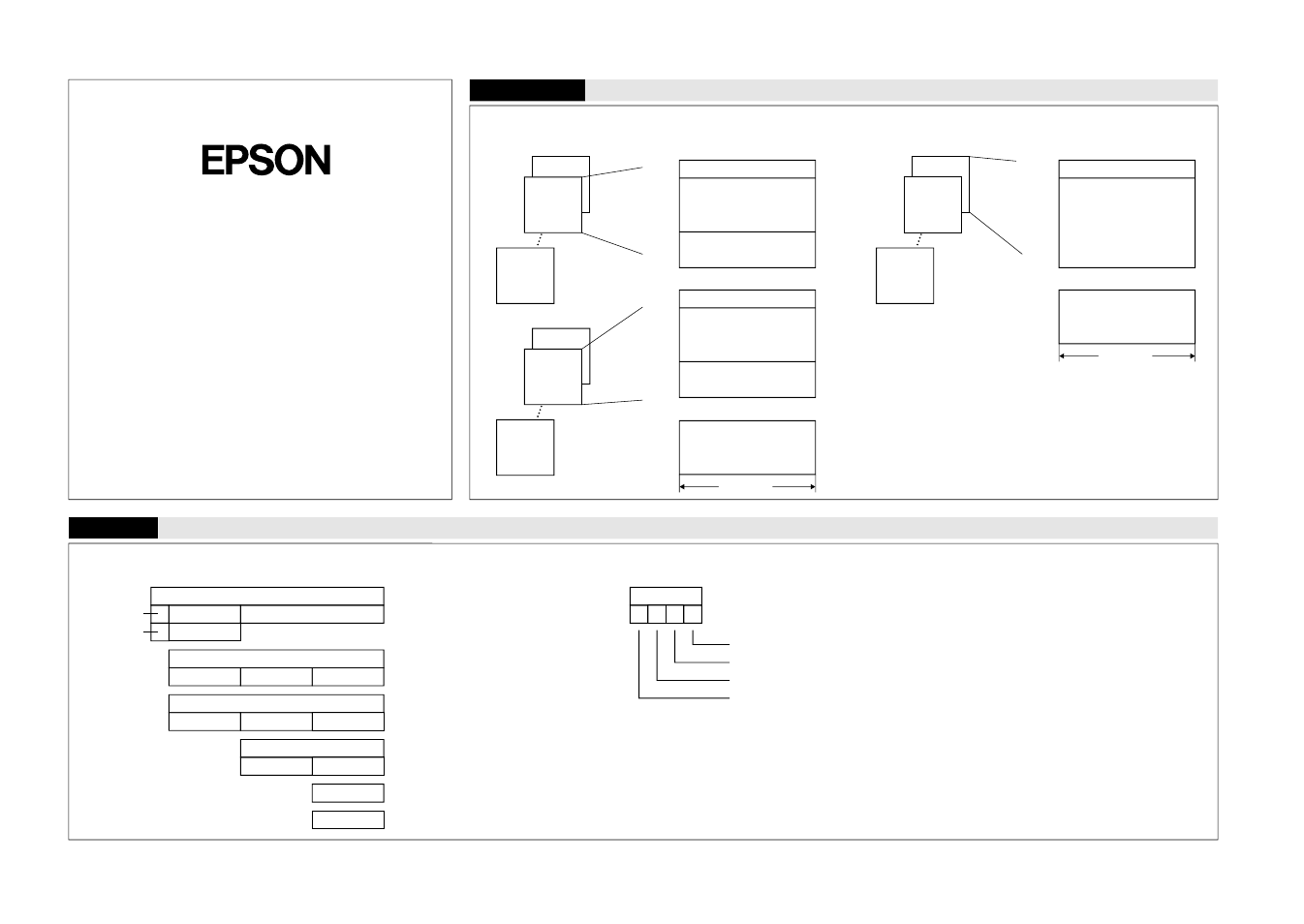

Memory Map

S1C6200 Core CPU

Program Memory Map

Registers

S1C6200 Core CPU

PC

IX

XP

PCP

XL

PCS

XH

IY

YP

YL

YH

SP

B

A

SPL

SPH

F

C

Z

D

I

0

3

0

3

4

7

8

11

12

Registers

Program counter

PCB

Flag register

Index register X

Index register Y

Stack pointer

Data register A

Data register B

Flags

I:

D:

Z:

C:

Interrupt flag

Decimal flag

Zero flag

Carry flag

(1: Enabled, 0: Disabled)

(1: Decimal adjustment on, 0: Decimal adjustment off)

(1: Zero, 0: Non zero)

(1: Carry/borrow, 0: No carry)

CMOS 4-bit Single Chip Microcomputer

S1C62 Family Assembler Package

Quick Reference

for Development

Step

0x0

0x1

0xf

0xff

(Maximum configulation)

(Maximum

configulation)

Data Memory Map

Page 0

Bank 0

Page 1

Page 15

Page 0

Bank 1

Page 1

Page 15

Program start address

Interrupt vector area

Program area

NPP

NBP

Page 1, Bank 0

Step

0x0

0xff

Program area

Other pages

Step

0x0

0x1

0xf

0xff

Interrupt vector area

Program area

Page 1, Bank 1

12 bits

Address

0x00

0x10

0xff

Page 0

Page 1

Page 15

Memory register area

RAM

Display memory

I/O memory

Page 0

Address

0x00

0xff

RAM

Display memory

I/O memory

Other pages

4 bits